Using MCU Power Management Options to Optimize System Efficiency

投稿人:电子产品

2013-11-13

When it comes to portable electronics, the length of operation on a single charge is very nearly as important as functionality. After all, it does not matter how much performance your device offers if the battery is dead. As a result, optimizing MCU power efficiency has climbed to the top rung of the designer’s to-do list. The process starts with today’s crop of highly-functional MCUs, with platforms specifically designed for lowest-power operation. Add in a variety of choices in power-saving modes like sleep, idle, and doze mode, among others, and functionality such as dedicated pins that automatically transition the system to backup battery when voltage is removed. Finally, throw the art of software development into the mix using tools like the IAR Embedded Workbench that show power consumption for the execution of each line of code. By reviewing the operation of the system in real time, developers can make informed trade-offs including modifying clock speed, putting the system into a lower power mode, and more.

If there is any lingering doubt about the importance of power efficiency in today’s embedded systems, look no further than the recent DRAM standards released by JEDEC. Not only did the organization release a new version of its portable-electronics standard in LPDDR3, its latest general DRAM standard, designated DDR4, includes a variety of features such as a pseudo-open-train architecture designed to reduce power consumption. Whether a microcontroller is embedded in a smartphone or an automobile, clearly to meet customer requirements it needs to deliver power-efficient operation.

To optimize power consumption, designers need to focus on two key objectives: minimize the amount of time spent in active mode, and minimize the amount of current required in nonactive mode. Not too long ago, controllers offered a single standby mode. Today, devices offer a range of options to increase the opportunity for systems to avoid active mode except when absolutely necessary. Let us now take a look at a few of these.

Power-saving modes

Microchip’s PIC24FJ128GA310 family of microcontrollers provides a range of power management options (Table 1). Sleep and Idle modes allow designers to shut down peripherals and/or the core to reduce power consumption while maintaining the ability for fast wake-up. In Retention Sleep mode, key circuits receive power from a separate low-voltage regulator. VBAT mode switches the system to operate off a backup battery in the event that VDD is removed, minimizing power consumption with RTCC. Deep Sleep without RTCC provides almost complete power down while maintaining software control so the device can be brought back up via external triggers. According to the company, it can operate on just 40 nA (3.3 V typ) compared to 400 nA at 32 kHz for RTCC mode.

- VBAT allows the device to transition to a back-up battery for the lowest power consumption with RTCC

- Deep Sleep allows near total power-down, with the ability to wake-up on external triggers

- Sleep and Idle modes selectively shut down peripherals and/or core for substantial power reduction and fast wake-up

- Doze mode allows CPU to run at a lower clock speed than peripherals

- Alternate Clock modes allow on-the-fly switching to a lower clock speed for selective power reduction

- Extreme Low-Power Current Consumption for Deep Sleep:

- WDT: 270 nA at 3.3 V typ

- RTCC: 400 nA at 32 kHz, 3.3 V typ

- Deep Sleep current, 40 nA, 3.3 V typ

Modifying clock speed can deliver important power savings. Doze mode allows the user to save power by manipulating clock speed, running the CPU at a lower clock speed than peripherals. The MCU also offers the option to switch on the fly to lower clock speeds to fine-tune power reduction.

The STM8L152C6T6 MCU from STMicroelectronics provides five low-power modes to allow users to balance among efficiency, performance, and startup time. In Wait mode, the CPU clock stops running but peripherals continue. The chip can be removed from Wait mode via an internal or external interrupt, a triggering event, or a reset. In Low-Power Run mode, the CPU performs certain functions along with select peripherals. Flash and data EEPROM are stopped while the system executes code from RAM at low speed. The system can move in and out of Low-Power Run mode via software. It can also exit via reset but not through interrupts.

In many embedded systems, MCUs spend a great amount of time waiting for an event to happen, which can squander power. The STM8L152C6T6 offers a Low-Power Wait mode, in which the CPU clock is stopped. A reset or an internal or external event generated by timers or I/O boards, will put the system back into Low-Power Run mode.

Active-Halt mode goes one step further, stopping the clocks for the CPU and all peripherals except for the RTC. External interrupts, RTC interrupts, or reset can be used to wake the system up from Active-Halt mode. Finally, Halt mode stops clocks for all peripherals and the CPU. The device remains powered up, maintaining data in RAM. An external interrupt or reset will wake the device. Select peripherals can also wake from Halt mode. The device can be configured to wait without the internal reference, allowing additional power savings by cutting off the internal reference voltage.

The Texas Instruments 16-bit MSP430FR5739 MCU offers seven low-power modes aimed at embedded systems in portable applications. At the top level, low-power mode 0 (LPM0) disables the CPU and the master clock while retaining all data. The peripheral clocks remain active and the user can choose the status of the submaster clock. At the high end of power savings, low-power mode 4.5 (LPM4.5) retains I/O pad state but does not retain data and disables the internal regulator. As part of its power-saving design, the MCU also integrates ferroelectric RAM for a lower-power nonvolatile memory.

Power debugging

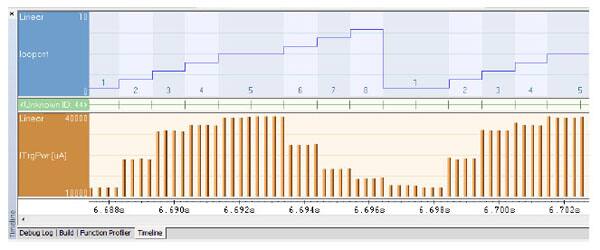

It does not matter how many power-saving modes an MCU has if they are not properly used. That is where power debugging tools like the I-Jet from IAR Software Systems come into play. The I-Jet samples the power consumption of the system as it runs, and IAR’s Embedded Workbench software package correlates that power data with the operation of the system.

In a perfect world, a developer could correlate a power spike directly to a line of code. The reality is that system capacitances spread consumption temporally, making it impossible to operate so discretely. The best choice is to view power usage as correlated to function. The timeline window displays power consumption as correlated to function calls (Figure 1). The user can then click on a power spike and trace it back to code.

With this degree of visibility, the developer can identify peripherals that are consuming power unnecessarily and perhaps adjust clock rate or put the system into a power-saving mode while it sits idle, and wake it up when it gets a response. This lets developers take advantage of their hardware’s power management options for best performance.

In summary, today’s embedded systems face demanding requirements for operation on a single charge. MCUs with a variety of built-in power management options, coupled with power debugging tools, can simplify optimization, freeing designers and OEMs to focus on their product’s core value proposition.

For more information on the parts discussed in this article, use the links provided to access product information pages on the DigiKey website.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。