在多相降压转换器中使用耦合电感器可提高效率

投稿人:DigiKey 北美编辑

2025-04-23

多相降压转换器广泛用于 12 V 应用,如数据中心、人工智能 (AI) 系统和通信基础设施。这些用例的一个共同主题是,需要在不影响性能或增加物理空间的情况下提高效率。

一种很有前景的方法是使用耦合电感器 (CL)。通过使用相间互感技术,CL 可出色的消除电流纹波,从而在保持兼容传统布局的同时显著提高效率。

本文将简要概述多相降压转换器设计人员在效率和布局方面面临的挑战。然后介绍 CL,给出验证效率提升的实验结果,并展示如何在 Analog Devices 的转换器中应用 CL。

传统多相降压转换器的效率挑战

在高性能计算和通信系统中,电力传输的效率损失会对系统成本、可靠性和热管理产生巨大影响。传统多相降压器的设计人员经常面临这方面的挑战,尤其是在轻载条件下,开关和 AC 损耗会变得更加明显。

同时,功率级布局和机械局限性也限制了提高性能的选项。在诸多系统中,元件尺寸的升级空间极为有限,且面对通用焊盘策略时,印刷电路板 (PCB) 布局的调整往往难以实现。

因此,人们对无需对电源架构进行重大修改就能实现更高效率的方法产生了浓厚的兴趣。理想情况下,此类解决方案应保持相同的焊盘布局,允许使用现有的输出电容 (CO),并能在各种负载条件下保持瞬态性能。

CL 通过减少纹波和改善开关损耗来满足这些需求,所有这些都与传统设计具有相同的焊盘布局。

CL 如何提升电源转换性能

在不改变布局的情况下,CL 为提高多相降压转换器的效率提供了有效途径。传统设计将每个相位视为电气独立的相位,与此不同的是,CL 共享标准磁结构,可实现相之间的相互作用。

这种相互作用受两个关键参数的制约:漏电感 (Lk) 和互感 (Lm)。漏电感的呈现与传统设计中的相电感 (L) 类似,而互感则会形成跨相位磁耦合。当流经某一相的电流增大时,会在其他相位产生一个与其电流变化相反的电压,从而显著消除纹波电流。

等式 1 和 2 确定了传统分立电感器 (DL) 设计 (dILDL) 和 CL 设计 (dILCL) 的预期纹波电流。这些电流取决于输入和输出电压 (VIN、VO)、电感 L、Lk 和 Lm、开关频率 (FS) 以及“品质因数”(FOM)。

等式 1

等式 1

等式 2

等式 2

其中:

ρ = 耦合系数 = Lm/L

D = 占空比

Nph = 耦合相数

等式 3 给出了 FOM 的计算方法。该等式反映了波纹消除程度与各种参数的函数关系。确切地说,FOM 取决于 ρ、Nph 和 D。

![FOM = (1 + ρ/ρ+1 x 1/Nph-1) / 1- [(Nph - 2 x j - 2) + j x (j+1)/ Nph x D + Nph x D x (Nph -2 x j-1) + j x (j +1)/Nph x (1 - D)] x ρρ+1/Nph-1 等式 3](http://sc-b.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2025/April/Use%20Coupled%20Inductors%20in%20Multiphase%20Buck%20Converters%20to%20Improve%20Efficiency/article-2025april-use-coupled-inductors-in-multiphase-equation3.jpg?la=en&ts=73a7c156-06a3-4b9c-aba7-4440849523dd) 等式 3

等式 3

其中:

j = floor (D× Nph)

虽然 FOM 取决于许多因素,但耦合系数 ρ 起着重要作用。为了说明这一点,我们不妨举一个实际例子。

评估耦合电感器的纹波电流

图 1 显示了电压输入 (VIN) 为 12 V、电压输出 (VO) 为 1 V、D 为 ~0.083 和传统 DL 值为 100 纳亨 (nH) 的应用中的 FOM 值。如需将此设计升级为 CL,同时保持相同输出 CO 的瞬态性能,CL 的 Lk 必须为 100 nH。这样,Lm 就成了设计变量。Lm 值越高,纹波越小,但保守估计,260 nH 的 Lm 值足以实现大部分所需的优势。

图 1:显示了在不同 Lm/Lk 值的情况下,4 相 CL 的 FOM 值随 D 变化的曲线,如图中突出显示部分所示。(图片来源:Analog Devices, Inc.)

图 1:显示了在不同 Lm/Lk 值的情况下,4 相 CL 的 FOM 值随 D 变化的曲线,如图中突出显示部分所示。(图片来源:Analog Devices, Inc.)

即使采用这种相当保守的设计,更少的纹波也足以实现较低的开关频率。这种情况如图 2 所示,该图比较了不同电感器配置和开关频率下的电流纹波。可以看出,工作频率为 400 千赫兹 (kHz) 的 CL 比工作频率为 800 kHz 的传统设计保持了更低的纹波。

图 2:VIN = 12 V 时,DL = 100 nH (800 kHz) 和 CL = 4 × 100 nH (800 kHz, 400 kHz) 的电流纹波与 VO 的函数关系。(图片来源:Analog Devices, Inc.)

图 2:VIN = 12 V 时,DL = 100 nH (800 kHz) 和 CL = 4 × 100 nH (800 kHz, 400 kHz) 的电流纹波与 VO 的函数关系。(图片来源:Analog Devices, Inc.)

开关频率的降低会直接导致开关损耗降低,其中包括晶体管开关损耗、MOSFET 体二极管的死区时间损耗、反向恢复损耗和栅极驱动损耗。随着开关频率的降低,这些与频率相关的损耗也会成正比地减少,从而大幅提高效率。

轻负载情况下,能效提升最为明显。由于交流损耗具有不受电流影响的固定特性,因此交流损耗会比较突出。而且,在整个负载范围内都具有这一优势。图 3 显示了 400 kHz 频率下使用耦合电感器的 8 相系统与在 600 kHz 频率下使用传统设计的 8 相系统的实验结果对比,峰值能效提高了约 1% ,满载效率提高了 0.5% 。

图 3:所示为具有相同封装的 8 相 DL = 100 nH(虚线)和 2 × CL = 4 × 100 nH(实线)设计的实测能效比。(图片来源:Analog Devices, Inc.)

图 3:所示为具有相同封装的 8 相 DL = 100 nH(虚线)和 2 × CL = 4 × 100 nH(实线)设计的实测能效比。(图片来源:Analog Devices, Inc.)

在不影响瞬态响应性能的情况下提高效率

值得注意的是,这些效率的提高并没有影响瞬态性能。图 4 所示为 4 相降压转换器的瞬态特性,比较了采用分立电感器的 8 相设计(600 kHz 时 DL = 100 nH)与采用两个 CL 时的配置波形,每个 CL 服务于 4 相(400 kHz 时 2 × CL = 4 × 100 nH),V IN = 12 V,V O = 0.9 V,负载阶跃为 135 A。使用相同的电流压摆率和 CO,会产生类似的瞬态响应。

图 4:所示为采用相同电路板,提供相同 CO 并在相同条件下,VIN = 12 V、VO = 0.9 V、针对 135 A 负载阶跃时的 8 相 DL = 100 nH (600 kHz) 和 2 × CL = 4 × 100 nH (400 kHz) 的瞬态响应。(图片来源:Analog Devices, Inc)

图 4:所示为采用相同电路板,提供相同 CO 并在相同条件下,VIN = 12 V、VO = 0.9 V、针对 135 A 负载阶跃时的 8 相 DL = 100 nH (600 kHz) 和 2 × CL = 4 × 100 nH (400 kHz) 的瞬态响应。(图片来源:Analog Devices, Inc)

虽然 CL 的较低开关频率通常会降低反馈带宽,但有两个因素可以消除这一限制:多相架构的固有优势和耦合设计形成的较大相位裕度。这种相位位裕度的改善是由于当占空比发生变化时,所有耦合相的电流都会同时响应一个相位的瞬态事件。

较低损耗可带来更好的热性能,进而提高长期可靠性,并有可能降低热受限系统的冷却要求。在实现了所有这些优势的同时,还能保持与现有布局的兼容性。

为多相降压转换器选择部件

要实现高效率多相降压转换器,可重点关注三个关键部件:稳压器控制器、功率级集成电路 (IC) 和 CL。其中,控制器管理相位的定时和同步,功率级处理大电流切换,CL 用于消除纹波,以实现更高的效率。

就控制器来说,Analog Devices 的 MAX16602GGN+T(图 5)是一个可靠的选择。该器件采用 56-QFN (7 mm × 7 mm) 封装,支持 8 相电源轨和单独的单相电源轨。该器件有多个显著特点:自主切相、通过 PMBus 进行遥测、集成故障保护和记录功能,以及内置 1.8 V 偏置稳压器。借助这些特性,这种控制器能够在多相稳压器系统中实现精确控制、减少组件数量并增强瞬态响应。

图 5:MAX16602GGN+T 稳压器控制器可支持多达 8 个相位。(图片来源:Analog Devices, Inc.)

图 5:MAX16602GGN+T 稳压器控制器可支持多达 8 个相位。(图片来源:Analog Devices, Inc.)

Analog Devices 的 MAX20790GFC+T 器件可用作功率级(图 6)。这款智能功率级将 MOSFET、栅极驱动器和电流检测功能集成在 12-FC2QFN (3.25 × 7.4 mm) 封装中。该器件的开关频率范围为 300 kHz 至 1.3 兆赫兹 (MHz),有助于设计人员优化 CL 设计的性能。该器件的主要功能包括:通过控制器 PMBus 进行遥测并报告故障、先进的自我保护功能。

图 6:MAX20790GFC+T 智能功率级在单器件中集成了 MOSFET、栅极驱动器和电流检测功能。(图片来源:Analog Devices, Inc.)

图 6:MAX20790GFC+T 智能功率级在单器件中集成了 MOSFET、栅极驱动器和电流检测功能。(图片来源:Analog Devices, Inc.)

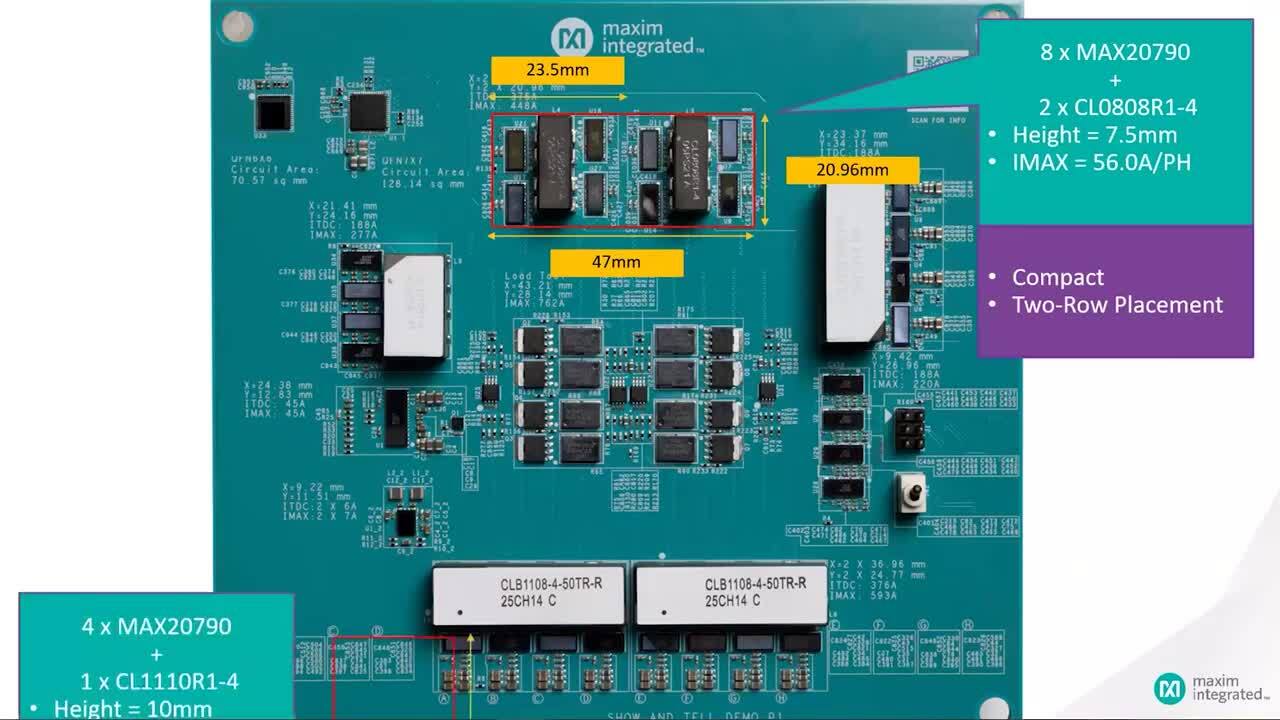

Eaton 的 CLB1108-4-50TR-R(图 7)就是一款合适的典型 CL,该器件在单封装中集成了四个紧耦合 50 nH 相位。该器件采用支持高饱和电流和高热性能的结构,因此非常适合要求苛刻的 AI 和数据中心的工作负载。

图 7:CLB1108-4-50TR-R 是一款 4 x 50 nH 耦合电感器。(图片来源:Eaton)

图 7:CLB1108-4-50TR-R 是一款 4 x 50 nH 耦合电感器。(图片来源:Eaton)

在典型配置中,MAX16602 控制器可驱动多达 8 个 MAX20790 功率级,每个输出相位都与双 4 相 CL 的相应绕组连接。与传统设计相比,这种架构在保持相同的物理尺寸和瞬态性能的同时,显著提高了效率。

利用评估硬件测试耦合电感器设计

对于希望探索 CL 解决方案的设计人员,Analog Devices 的 MAX16602CL8EVKIT# 评估套件(图 8)为测试和开发提供了一个便捷的平台。该电路板专门用于演示 MAX16602 控制器和 MAX20790 功率级 IC、耦合电感器配合使用时的功能。

图 8:MAX16602CL8EVKIT# 可用于探索多相降压转换器设计。(图片来源:Analog Devices, Inc.)

图 8:MAX16602CL8EVKIT# 可用于探索多相降压转换器设计。(图片来源:Analog Devices, Inc.)

评估套件是一个实用型参考设计,用于展示如何有效地集成这些组件。评估套件包括支持 8 相电源转换解决方案所需的全部电路,并集成了全面的测量点,可对瞬态响应等关键参数进行监测。

结语

CL 为多相降压转换器设计带来了显著优势。通过在相位间引入互感,这些组件能够消除大量纹波电流,从而降低开关频率,提高总效率。重要的是,在实现这些优势的同时,不会增加物理占用空间或影响瞬态性能。这些解决方案与控制器、功率级芯片组相结合,为设计人员从传统拓扑结构过渡到更高效的磁耦合替代方案提供了一条切实可行的途径。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。