使用单个超低功率 HMP 处理器来运行实时处理和应用处理工作负载

投稿人:DigiKey 北美编辑

2019-08-06

消费者希望个人电子产品和其他移动设备不仅能提供更快的响应速度和更出色的功能,同时还能提供更长的电池寿命。但对于开发人员而言,很多应用的实时响应和高性能要求决定了只能使用单独的处理器来满足这些相互冲突的需求。这会增加成本、功率和空间,还会提高硬件布局和软件的复杂性。

更好的方法是将必需的硬件集成到单个芯片中。我们可以借助异构多核处理 (HMP) 器件。这些处理器包含多个不同类型的内核,具备包括性能优化、低功耗、改进型系统安全性和可靠性等诸多优势。

本文介绍开发人员如何使用 NXP Semiconductors 的异构多核处理器来满足这些混合工作负载需求,同时不影响低功率和降低设计复杂性的要求。

不断变化的要求

传感器技术和数据处理算法的进步为开发人员创造了很好的机会,让他们能够管理实时数据采集和计算密集型算法执行这两种相互冲突的需求。过去,开发人员通常将这些工作负载划分到单独的系统中。

在网络层次结构的最底层,嵌入式处理器(例如基于 Arm® Cortex®-M4 内核的处理器)会收集数据,在实时操作系统 (RTOS) 或裸机系统上运行优化代码。在该层次结构的较高层,高性能应用处理器(例如基于 Arm Cortex-A7 内核的处理器)会依次执行数据分析算法,在熟悉的 Linux 或 Android 等操作系统上运行应用代码。

随着边缘计算系统的兴起,应用代码的执行已转移到更接近数据源的位置。事实上,更复杂的分析算法需要更快的响应速度,现已促使应用处理需求被转移到终端设备自身之上运行。消费者日益希望将先进分析功能(包括人工智能方法)内置到设备中,例如物联网 (IoT) 传感器、可穿戴设备和其他低功率产品。

异构多核处理的角色

HMP 器件将嵌入式处理器和应用处理器内核整合在一起,它的出现帮助开发人员在很多应用中更高效地处理混合工作负载。HMP 处理器集成了不同的内核,每个内核经过优化,可满足与目标产品的工作负载相关的不同要求。使用 NXP 的 i.MX 7ULP 系列超低功率处理器,开发人员能够利用 HMP 架构的强大性能,满足消费者对下一代 ULP 产品提出的高性能和更长电池寿命的严苛需求。

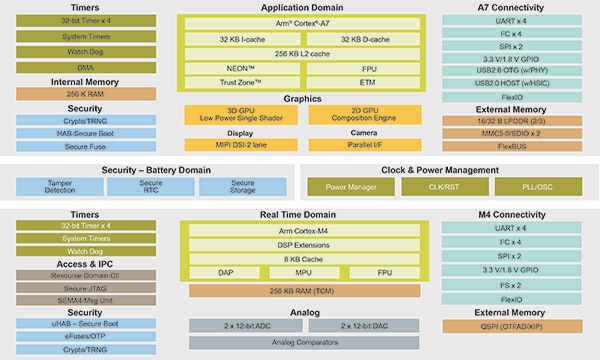

i.MX 7ULP 处理器提供消费级 (MCIMX7U5DVP07SC) 和工业级 (MCIMX7U5CVP06SC) 版本,将异构内核与图形处理单元、安全加速器、存储控制器和全套外设接口集成在一起(图 1)。

图 1:除了丰富的模块和外设之外,NXP 的 i.MX 7ULP 应用处理器系列还将用于实时处理的 Arm Cortex-M4 内核与用于应用处理的 Arm Cortex-A7 内核整合在一起。该系列使用单独的电源域来优化功率和性能。(图片来源:NXP)

图 1:除了丰富的模块和外设之外,NXP 的 i.MX 7ULP 应用处理器系列还将用于实时处理的 Arm Cortex-M4 内核与用于应用处理的 Arm Cortex-A7 内核整合在一起。该系列使用单独的电源域来优化功率和性能。(图片来源:NXP)

NXP 的 i.MX 7ULP 系列专为功率受限的便携式设备而设计,将 Arm Cortex-A7 内核和 Cortex-M4 内核整合在一起并分别由单独的电源域供电,以满足新兴的应用要求。此外,通过使用不同的电源岛,可让不同的模块在不被需要时有选择地断电。如下所述,借助 i.MX 7ULP 器件集成的先进电源管理功能,开发人员可以使用这些电源域和电源岛来调节性能和功耗,以适应他们的应用。

功率优化

在设计 i.MX 7ULP 系列时,NXP 将功率和性能优化功能集成到这些器件中,从芯片设计层开始一直贯穿整个架构。

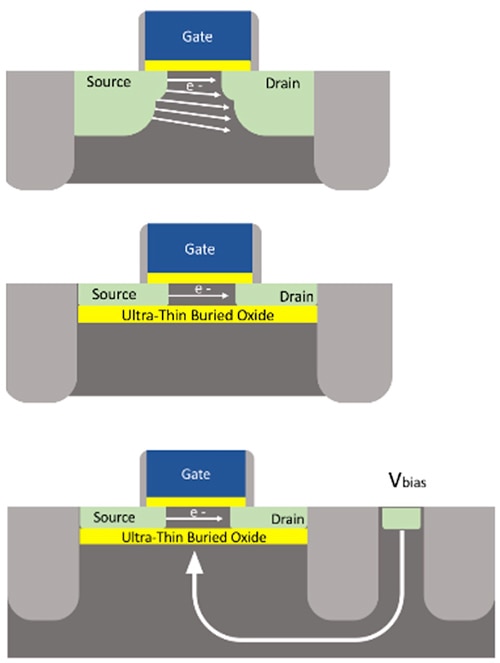

在最底层,i.MX 7ULP 系列将可减少漏电电流的制造方法与可降低寄生效应的晶体管几何形状相结合,从而降低了动态功耗。与常规晶体管结构(图 2,上)不同,i.MX 7ULP 器件使用超薄埋氧层制造(图 2, 中),可减少从源极到漏极的电子流动,从而减小漏电电流;进行进一步的增强,让设计人员能够增加正向偏置 (FBB) 或反体偏置 (RBB)(图 2, 下)。

图 2:当电子从源极流向漏极时,常规晶体管可能出现严重漏电(上),但 NXP 的 i.MX 7ULP 系列是使用超薄埋氧层制造的,该层能够阻碍电子流动(中),该器件的结构能够通过正向偏置 (FBB) 或反向偏置 (RBB) 进一步加快或减慢电子流动(下)。(图片来源:NXP)

图 2:当电子从源极流向漏极时,常规晶体管可能出现严重漏电(上),但 NXP 的 i.MX 7ULP 系列是使用超薄埋氧层制造的,该层能够阻碍电子流动(中),该器件的结构能够通过正向偏置 (FBB) 或反向偏置 (RBB) 进一步加快或减慢电子流动(下)。(图片来源:NXP)

如果优先考虑能效,开发人员可以利用 RBB 来减少电子流动,并以性能下降为代价,进一步减小漏电电流和整体器件功耗。相反,开发人员可以利用 FBB 来增强电子流动,以增加功耗为代价(因为漏电电流更高)来提高性能。

在芯片设计层,i.MX 7ULP 系列采用了多种技术,包括动态频率调节 (DFS)、动态电压调节 (DVS)、基于软件的时钟选通和基于软件的电源选通。除了降低不同外设的功耗之外,开发人员还能利用这些功能,有选择地关闭内部存储器模块,或将存储器置于不同的节能模式。

在架构层上,由于采用多电源域(包括前文所述的用于 Cortex-A7 和 Cortex-M4 子系统的单独电源域),因此调节功率和性能的能力得以进一步提升。

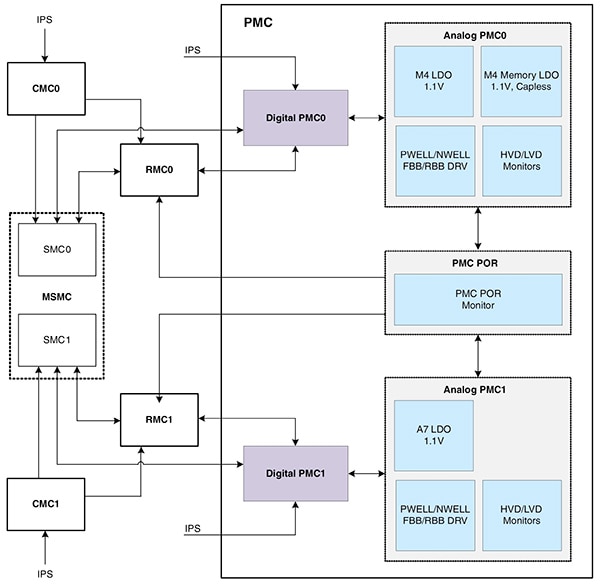

每个处理器内核的电源域都包括 FBB 和 RBB 驱动器、专用低压差 (LDO) 稳压器,以及旨在提示电源漂移高于或低于指定阈值的高电平检测器 (HVD) 和低电平检测器 (LVD) 监测器。单独的上电复位 (PoR) 监测器用于跟踪始终开启 (always-on) 的电源域中的电压电平。

搭配单独的内核电源域,个别电源域可用于控制系统功能(例如始终开启的硬件),而电池供电的电源域则用于管理关键功能的电源,包括实时时钟和安全非易失性存储模块等。与内核电源域一样,这些专用电源域分别支持一系列广泛的专用节能功能(这些功能数量太多,无法在本文中逐一介绍)。

举例来说,用于始终开启功能的电源域包括低漏电唤醒单元 (LLWU) 模块,它让开发人员能够使用多个外部引脚或内部模块,作为下文介绍的特殊低漏电功率模式的唤醒源。

这些架构功能集成在器件的集成式电源管理控制器 (PMC) 中,可处理这些单独的电源域以及器件的电源岛(图 3)。

图 3:NXP 的 i.MX 7ULP 系列集成了先进的控制功能,让开发人员能够通过编程方式配置电源域和电源岛,以调节功率和性能,满足不断变化的应用要求。(图片来源:NXP)

图 3:NXP 的 i.MX 7ULP 系列集成了先进的控制功能,让开发人员能够通过编程方式配置电源域和电源岛,以调节功率和性能,满足不断变化的应用要求。(图片来源:NXP)

使用这种方法,开发人员通过普通的智能外设子系统 (IPS) 总线向一个复杂的控制装置发送命令,启动功率模式转换,其中的控制装置包括三个紧密耦合的模块:

- 内核模式控制器 (CMC),用于支持多种内核功能

- 多核系统模式控制器 (MSMC),包括用于 Cortex-M4 电源域的系统模式控制器 0 (SMC0) 和用于 Cortex-A7 电源域的 SMC1,可处理不同功率模式之间的定序,监视用于启动功率模式转换的事件,以及整体控制与功率优化相关的电源、时钟和存储器功能

- 复位模式控制器 (RMC),用于处理芯片复位功能

调节功率和性能

对于所有的电源管理功能,i.MX 7ULP 都为开发人员提供了他们熟悉的编程模型。与其他高级处理器一样,i.MX 7ULP 器件通过一系列可编程低功率模式,实现不同的低功率工作状态。事实上,i.MX 7ULP 处理器内核支持多种软件控制的低功率模式,以便开发人员尽可能将功耗降至符合所需功能要求的最低水平。

利用这些不同的低功率模式,开发人员可以将一个或两个内核及其子系统设置为正常运行模式、等待模式、停止模式的不同变化形式。

正常运行模式和高速 HSRUN 模式下可以提供高性能,以支持应用的计算密集型部分。在 HSRUN 模式下,内核子系统以最高频率工作。如果应用能够接受较低性能,开发人员可将内核设置为超低功率运行 (VLPR) 模式,在最高 48 MHz 的频率下运行,相应地实现更低功耗。

在正常等待模式下,外设完全工作,但内核使用时钟选通,在静态状态下等待,并在收到等待中断 (WFI) 信号时随时唤醒。利用这种模式,开发人员可让自主外设操作填充缓冲器,或使用直接存储器访问 (DMA) 事务填充系统存储器,然后再发出中断,让内核退出等待状态。超低功耗等待 (VLPW) 模式允许外设以较低的频率继续工作,但对内核时钟使用门控。

在可穿戴设备或便携式设备等应用中,系统可能长期面临无活动状态,并定期被猝发活动中断。这类情况下,节能能力对电池寿命至关重要。当应用能够接受较慢的内核唤醒速度时,可将器件置于比运行、等待或超低功率变化模式更深的休眠状态,这是一个特别有效的选项。为了支持这种方法,开发人员可以将每个 i.MX 7ULP 内核子系统置于更深的休眠状态,当处于这些状态时,唤醒时间各不相同:

- 在停止状态下,有些外设能够以异步方式工作,但内核保持静态状态,对于 Cortex-A7 和 Cortex-M4 的唤醒时间皆为 7 μs

- 在超低功耗停止 (VLPS) 模式下,外设工作进一步受到限制,但内核保持静态状态,对于 Cortex-A7,唤醒时间为 21.5 μs,对于 Cortex-M4 为 9 μs。

对于功耗要求更严格的应用,开发人员可将每个内核设置为以下会关闭更多器件子系统的特殊低漏电模式:

- 低漏电停止 (LLS),对内核、总线和外设使用时钟选通,让内核处于 WFI 状态下,对于 Cortex-A7,唤醒时间为 40 μs,对于 Cortex-M4 为 58 μs

- 超低漏电停止 (VLLS),对内核的整个电源域使用时钟选通,导致唤醒时间更长,对于 Cortex-A7,唤醒时间为 60 μs,对于 Cortex-M4 为 375 μs

为了进一步节省电能,开发人员可在 VLPS 和 LLS 等功率模式下使用 RBB,此时性能会有相应降低,而唤醒时间则会递增大约 2 至 4 μs。

相反,如果需要处理计算密集型工作负载,开发人员可在特殊高速运行 (HSRUN) 模式下运行内核。HSRUN 模式可将 Cortex-A7 内核从正常的 500 MHz 工作频率提高到过驱模式下的 720 MHz 运行频率。

凭借这种精细的控制水平,开发人员可以配置 i.MX 7ULP 来满足更极端的功率要求,而不牺牲关键功能。例如,某个应用需要达到尽可能低的功耗,但又需要 Cortex-M4 内核的实时功能,以及使用特定的 Cortex-A7 子系统外设或存储器。这种情况下,开发人员可以将 Cortex-A7 子系统置于停止或 VLPS 状态,Cortex-M4 内核在执行实时操作时访问 Cortex-A7 的存储器或外设。为了进一步节省电能,开发人员可使用 Cortex-M4 时钟来驱动 Cortex-A7 的外设。

简单的系统实现

要使用 i.MX 7ULP 实现低功率系统,开发人员可以选择可用的软件可编程功率模式和配置,以匹配功率和性能要求。在硬件方面,系统设计甚至更加简单。

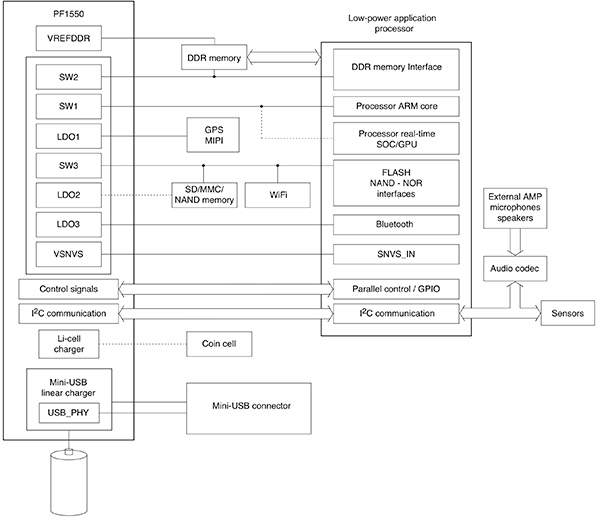

对于典型应用,开发人员只需将 i.MX 7ULP 处理器与配套的 NXP MC32PF1550A3EPR2 电源管理 IC (PMIC) 组合在一起来完成设计,便能处理混合工作负载,而不会影响有限的功率预算(图 4)。

图 4:NXP 的 MC32PF1550A3EPR2 电源管理 IC 提供了 NXP 的 i.MX 7ULP 处理器所需的整套电源,从而将硬件设计简化为这两个器件和少数无源元器件的简单组合。(图片来源:NXP)

图 4:NXP 的 MC32PF1550A3EPR2 电源管理 IC 提供了 NXP 的 i.MX 7ULP 处理器所需的整套电源,从而将硬件设计简化为这两个器件和少数无源元器件的简单组合。(图片来源:NXP)

MC32PF1550A3EPR2 专为支持 NXP 处理器(比如 i.MX 7ULP 系列)的供电需求而设计,集成了三个开关模式降压稳压器(SW1、SW2、SW3)、三个 LDO 稳压器(LDO1、LDO2、LDO3)、一个存储器基准电压电源、一个完整的单芯锂离子充电器,以及用于器件配置的一次性可编程 (OTP) 存储器。

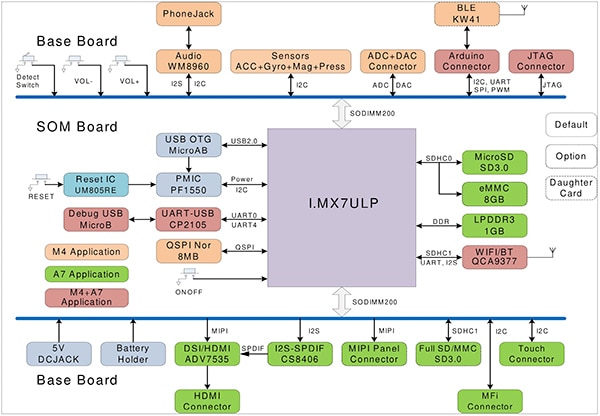

借助 MCIMX7ULP-EVK 评估套件,NXP 演示了组合 MC32PF1550A3EPR2 PMIC 和 i.MX 7ULP 器件所需的简单硬件接口。除了搭载 i.MX 7ULP 处理器和 MC32PF1550A3EPR2 PMIC 的系统级模块 (SOM) 电路板之外,该套件还包括一个基板,上面带有多个传感器、无线功能、音频编码解码器、SD 连接器,以及包括 JTAG 和 Arduino 在内的其他多个连接器(图 5)。

图 5:MCIMX7ULP-EVK 评估套件将搭载 i.MX 7ULP 处理器和 MC32PF1550A3EPR2 PMIC 的系统级模块电路板与一个基板整合在一起,基板上包含了传感器、连接器以及利用 i.MX 7ULP 器件加快软件开发所需的其他元器件。(图片来源:NXP)

图 5:MCIMX7ULP-EVK 评估套件将搭载 i.MX 7ULP 处理器和 MC32PF1550A3EPR2 PMIC 的系统级模块电路板与一个基板整合在一起,基板上包含了传感器、连接器以及利用 i.MX 7ULP 器件加快软件开发所需的其他元器件。(图片来源:NXP)

评估套件提供了开箱即用的功能,同时 NXP 还为开发人员提供了可下载的设计文件、工具和用于定制软件的板级支持包(使用 FreeRTOS 运行实时代码,使用 Linux 或 Android 运行应用代码)。

总结

在移动产品中,消费者既需要更先进的功能,又要求更长的电池寿命,这迫使开发人员过去不得不在功率和性能方面进行一定程度的折衷。另外,消费者越来越希望从物联网设备、可穿戴设备和其他便携式产品中的更多传感器及时获取数据,这也迫使开发人员在实时功能和应用级性能之间进行进一步的折衷。

但是,如本文所述,开发人员可以转而采用 HMP 架构,例如 NXP 的 i.MX 7ULP 处理器系列中所用的架构,在不牺牲功能的情况下满足严格的超低功率要求。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。