直接数字合成器DDS基础知识

投稿人:DigiKey 北美编辑

2019-03-20

随着无线设备数量的激增,设计人员正在使用越来越复杂多变的波形,来满足应用在数据速率、干扰抑制、成本、封装和低功耗方面的要求。这些波形需要有稳定的射频源:可以根据需要进行调谐,而且同时具有频率和相位捷变性。同时,射频源还必须能够提供高信号纯度。满足这些要求的解决方案就是直接数字合成器 (DDS)。

DDS 使用数字方法产生模拟波形,使其能够利用数字方法的可编程性、更高的集成度和更低的成本。此外,DDS 可实现几乎瞬时的频率或相位改变,因此成为先进的数字调制技术(如频移键控 (FSK) 和扩频)以及干扰抑制技术(如跳频)的主要来源。因此,DDS IC 正在迅速取代或增强传统的锁相环 (PLL) 和其他模拟射频源,同时仍然可提供高稳定性和信号纯度。

本文将介绍 DDS 技术的基础知识以及如何指定 DDS IC。然后,将介绍一些合适的 DDS IC 解决方案,说明如何有效地应用它们。

直接数字合成的工作原理

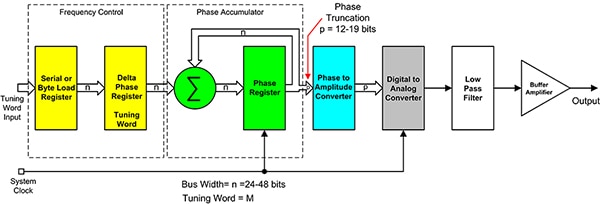

数字合成以相位累加器为基础,累加器可生成一系列数字状态,其值呈线性增长而形成数字斜坡信号。这一信号具有周期性,表示输出波形的瞬时相位,弧度范围为 0 到 2p。这是查找表的数字输入;查找表用于将数字斜坡信号转换为正弦波(图 1)。尽管最常见的 DDS 输出波形是正弦波,但也容易产生斜坡信号、三角波和方波。

图 1:直接数字合成器基于相位累加器,累加器可产生波形瞬时相位。查找表提供了相幅转换,该转换应用于数模转换器,经过滤波后产生所需的模拟输出。(图片来源:DigiKey)

相幅转换查找表的输出会发送到数模转换器 (DAC),并转换成模拟波形,即最常见的正弦波。由于 DAC 的输入是一系列采样值,因此输出具有量化步长。这些步长在频域内以采样率的倍数产生频谱图像,而这些图像是不需要的。在 DAC 之后放置低通滤波器,便能抑制这些不需要的频谱响应。

相位累加器

相位累加器是一种模 N 计数器,具有 2N 个数字状态,这些状态会在每个系统时钟输入脉冲发生时逐渐递增。增量的大小取决于应用于累加器相加级的调谐字 M 的值。该调谐字确定了计数器增量的步长。这将决定输出波形的频率。

相位累加器的长度通常为 24 - 48 位;24 位累加器共有 224(即 16,777,216)个状态。这一数字表示 0 到 2p 弧度之间的相位值数量,或者说是可实现的相位增量。对于 24 位相位累加器,相位分辨率为 3.74 E-7 弧度。如果使用更大的相位累加器,相位增量会变得更加精细。

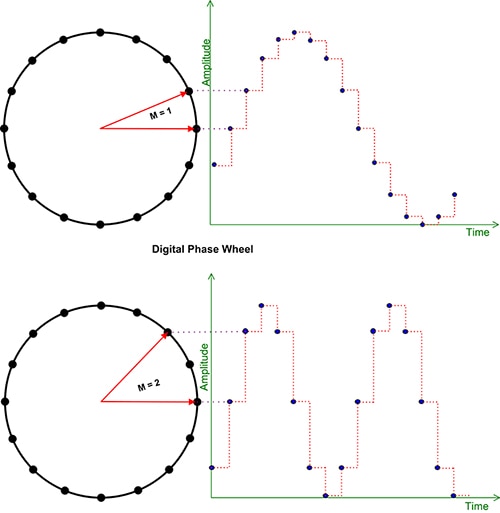

直观显示相位累加器运行情况的一种方法是,将累加器运行看作一个相位轮(图 2)。

图 2:16 状态相位累加器运行的简化图,使用相位轮来直观显示调谐字如何影响 DDS 的输出频率。(图片来源:DigiKey)

累加器状态具有周期性,显示为一个圆圈上的点。这些点表示累加器的各个相位状态。在本例中,为简单起见,假设累加器有 16 个状态。如上方的图所示,如果调谐字等于 1,那么每个时钟的步长增量均为 1,而且在整个周期内选中了所有状态。

相位轮的右侧显示的是每个状态的模拟输出。由于这是一个量化器件,因此模拟输出将保持其当前状态,直到时钟将相位轮推进到下一个状态。输出波形由包含 16 个值的单个量化正弦波周期组成。

在下方的图中,调谐字的值设置为 2。这时的相位轮上每隔一个状态被选中。对应的模拟输出由两个周期组成,每个周期有 8 个幅值,因此总共有 16 个状态。由于调谐字设置为 2,因此输出频率现在是之前所获值的两倍。

DDS 的输出频率由调谐字的值设定,并且按调谐字的值成比例地增加。采样率在系统时钟速率下保持不变,而且输出采样之间的时间恒定。输出频率取决于调谐字增量,因此随着调谐字的值增大,每个输出周期中的步长数会减少,从而增加了频率。调谐字可以增大到每个周期只有两个采样点,从而使 DDS 输出达到其奈奎斯特频率,即系统时钟速率的一半。通常,DDS 在设计上限制为输出频率总是小于奈奎斯特极限值。

除了系统时钟频率,DDS 的输出频率还取决于调谐字的值和累加器的长度。该输出频率由等式 1 表示:

![]() 等式 1

等式 1

其中:

fout 表示 DDS 输出频率

M 表示调谐字的值

fc 表示系统时钟频率

N 表示相位累加器的长度

相位累加器的输出是输出波形的瞬时相位,用来驱动相幅转换器。相幅转换器可输出一个数字值,其值为输入相位的正弦波形幅度。

请注意,用于驱动相幅转换器的位数小于用于相位累加器的位数。这种情况称为相位截断,用来减少相位累加器后面的数字级芯片面积和功耗。虽然这确实会导致一些杂散的频谱成分(称为截断杂散),但经过精心设计后可达到最小化。

使用输出低通滤波器的原因

图 2 所示的波形由于其阶跃特性而富含谐波。因此,必须使用低通滤波器来消除这些频谱谐波,以及 DDS 中其他工艺产生的其他杂散频率响应。

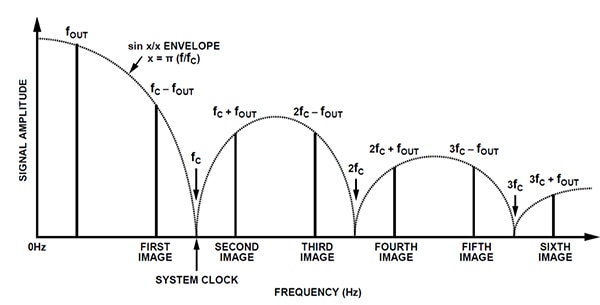

例如,图 3 显示了一个器件在时钟频率为 fc、输出频率小于 fc/2 时的 DDS 输出频谱。该输出频谱显示了输出频谱线 fout,及其高于和低于时钟频率的镜像频率,还有高达和超过第三次谐波的所有谐波。

图 3:系统时钟频率为 fc、输出频率为 fout 的 DDS 频谱图,显示高达时钟第三次谐波的输出频率成分。(图片来源:Analog Devices)

DDS 输出频率范围为 0 Hz 到奈奎斯特极限 fc/2。sin(x)/x 整形是由于时域中的量化信号而引起,如图 2 所示。sin(x)/x 函数的零值发生在时钟频率及其所有谐波处。要在输出范围内提高幅度平坦度,可通过幅值校正来取消 sin(x)/x 整形。

为了显著减小超过奈奎斯特频率的频谱成分幅度,采用了具有高于 DDS 频率范围的锐截止特性的低通滤波器。如果将 DDS 频率范围扩展到奈奎斯特频率,则滤波器需要无限陡的截止斜率,以便排除时钟频率的低镜像频率,否则会与奈奎斯特频率重叠。这也是 DDS 频率范围很少扩展到奈奎斯特频率的一个原因。

使用商业 DDS IC 进行设计

在选择和使用 DDS 时需要考虑很多因素。首先,要考虑应用所需的必要功能:所需的频率范围、幅度和偏移范围、波形、分辨率和调制能力。信号纯度通常是选择信号源时考虑的因素。无杂散动态范围 (SFDR)、总谐波失真 (THD) 和相位噪声都是重要的参数,同样重要的还有功耗,尤其是在移动应用中。

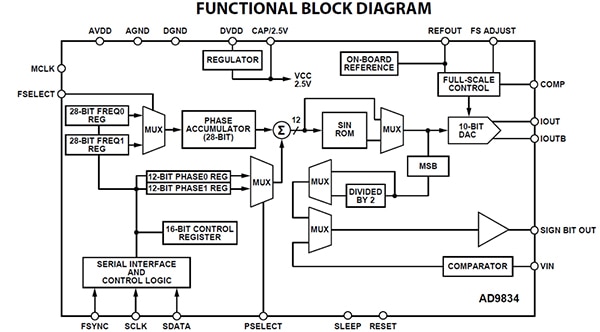

低功耗 DDS 的一个良好范例是 Analog Devices 的 AD9834BRUZ-REEL7(图 4)。该器件由一个三线串行接口控制,使用一个 3 伏电源,功耗仅为 20 毫瓦 (mW)。它能够输出正弦、斜坡和方波函数,最大时钟频率为 50 兆赫 (MHz),在图中显示为数字时钟输入 MCLK。根据之前的奈奎斯特讨论,该时钟频率意味着它可以输出最高 25 MHz 的波形。

图 4:Analog Devices 的 AD9834 低功耗 DDS 内部功能示意图。该器件使用一个 3 V 电源,功耗仅为 20 mW,能够生成最高 25 MHz 的正弦、斜坡和方波函数。(图片来源:Analog Devices)

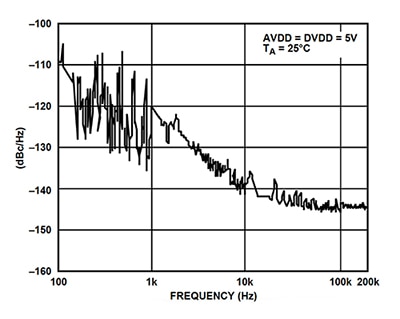

相位累加器的长度为 28 位,在 50 MHz 的时钟频率下产生 0.186 Hz 的频率分辨率。相位噪声也取决于 MCLK 输入的质量,显示为载波偏移的函数(图 5)。若是 AD9834,对于 2 MHz 的 FOUT 和 50 MHz 的 MCLK,在载波偏移为 1 kHz 时,相位噪声为 -120 dBc/Hz。

图 5:相位噪声取决于 MCLK 的质量,对于 2 MHz 的 FOUT 和 50 MHz 的 MCLK,在载波偏移为 1 kHz 时,相位噪声显示为 -120 dBc/Hz。(图片来源:Analog Devices)

内置 DAC 的分辨率为 10 位,而窄带 SFDR 通常优于 -78 dB。

AD9834 的特点包括双频和相位寄存器,因此既支持调频,也支持调相。此外,可以绕过正弦只读存储器 (ROM),而使用相位累加器输出来驱动 DAC 生成斜坡函数。输出引脚可提供符号位,该位可用于提供方波来生成时钟。

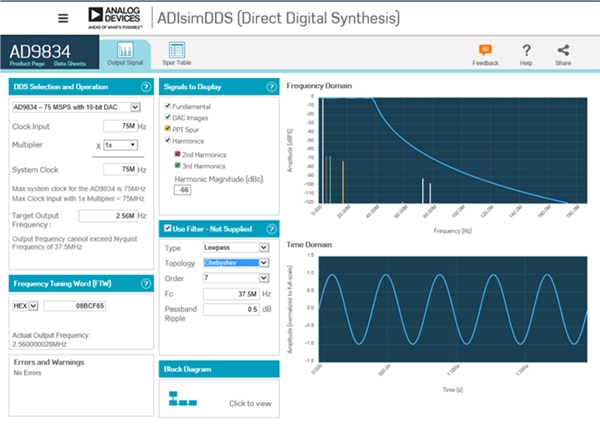

为了帮助设计工作,供应商通常会提供精选的工具来简化工作。AD9834 DDS 由 Analog Devices 的 ADIsimDDS 提供支持,这是一个交互式在线设计工具,可帮助设计人员评估各种配置,包括输出频率、调谐字和基准时钟(图 6)。

图 6:利用 Analog Devices 的 ADIsimDDS 交互式设计工具,设计人员可以试验各种 DD 配置和滤波选择。(图片来源:Analog Devices)

ADIsimDDS 程序首先提示选择特定的 DDS 产品,在本例中是 AD9834。在用户输入系统时钟频率和所需的输出频率后,该程序将计算相位累加器的调谐字。频域显示器将显示 DDS 输出的频谱,包括输出信号、谐波、DAC 镜像、时钟谐波和时钟镜像。若要了解不同滤波器对输出频谱的影响,可以对 DDS 输出应用滤波器仿真器。

如果设计需要更高的性能和频率,可以选择 Analog Devices 的 AD9952YSVZ-REEL7,其最大时钟频率为 400 MHz,可以产生最高 200 MHz 的正弦信号,而相位噪声较低,在 160 MHz(±100 千赫 (kHz) 偏移)AOUT 时 SFDR 指定为大于 80 dB。如果直接与 AD9834 相比较,其窄带 SFDR 在 20 MHz 时通常为 -70 dB,当然这取决于频率。

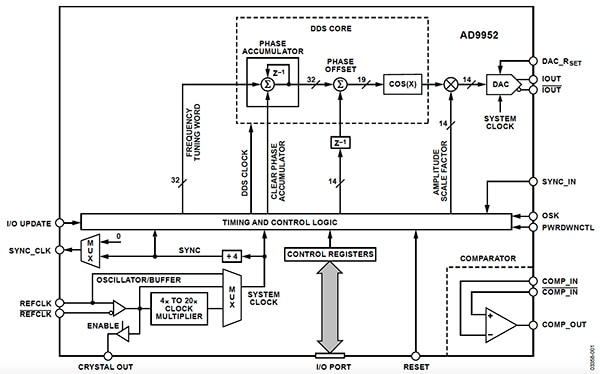

AD9952 不使用 MCLK 输入。相反,它有内置时钟振荡器及关联的 PLL 倍频器,后者可以使用单个外部晶体,将时钟频率倍增 4 到 20 倍(图 7)。该 DDS 拥有自己的内部系统时钟(最高 400 MSPS),因而能够实现低相位噪声(1 kHz 偏移时 ≤ -120 dBc/Hz)。

图 7:AD9952 采用外部晶体的输入,并产生自己的内部系统时钟,以更好地控制更高性能所需的条件,如较低的相位噪声。(图片来源:Analog Devices)

AD9952 还具有 32 位相位累加器和 14 位 DAC。该 DDS 通过串行接口进行控制。

对于更宽的频率范围,可以选择 Analog Devices 的 AD9957BSVZ-REEL,能支持最高 1 千兆赫 (GHz) 时钟速率,输出频率最高 400 MHz,适用于高级通信应用。该器件使用 32 位相位累加器和 14 位高速 DAC,主要用作正交调制器,可产生由八个相位/频率寄存器控制的同相 (I) 和正交 (Q) 成分。它们可用于在输出端生成正交调制数据流。可选的逆 SINC (sin(x)/x) 滤波器可用来补偿前面讨论的 sin(x)/x 整形。

以上是三个已上市销售的 DDS 集成电路的例子,这些电路的功能涵盖从简单到复杂的信号生成。

总结

随着设计人员不断面临改善无线系统性能、尺寸、成本和功耗的挑战,DDS 已证明是一个不错的选择。它们为信号生成带来了数字稳定性、捷变性和可重复性,可提供多种输出波形和先进的调制能力,包括跳频和相位跳变。随着这些 DDS 进入设计人员的工具包,供应商也在通过使用高级工具来简化选择和集成工作,从而缩短设计过程。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。