专为边缘计算应用设计的中端视觉 AI 微处理器

投稿人:DigiKey 北美编辑

2025-07-17

边缘 AI 应用通过计算机视觉算法,实时检测人员、物体或缺陷等异常情况。在边缘设备上处理图像和视频通常需要视觉 AI 微处理器 (MPU)。这种处理器能连接摄像头,运行 AI 模型,并且通常内置专用的 AI 加速器。

将视觉 AI 功能集成到单个设备中,可降低所用独立组件的成本和体积,使先进的视觉 AI MPU 成为紧凑型嵌入式应用的理想之选。

Renesas Electronics Corporation 推出的 RZ/V2N MPU(图 1)是一款视觉 AI MPU,具备低功耗、高 AI 推理能力、四颗 Arm® Cortex-A55 CPU (1.8 GHz)、一颗 Arm Cortex-M33 (200 MHz) 以及通过 MIPI 接口连接的两个摄像头输入。

图 1:Renesas 的 RZ/V2N MPU 为设计人员在边缘应用中集成视觉 AI 提供了新选择。(图片来源:Renesas Electronics Corporation)

图 1:Renesas 的 RZ/V2N MPU 为设计人员在边缘应用中集成视觉 AI 提供了新选择。(图片来源:Renesas Electronics Corporation)

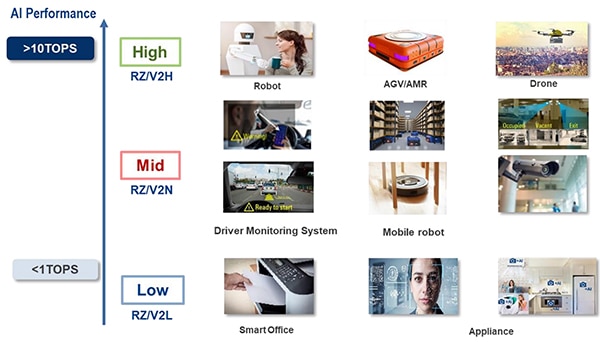

这款 Renesas MPU 是针对边缘应用的性价比之选,能以经济实惠的价格提供中高端 AI 功能。这款器件属于该公司的 RZ/V 系列的产品之一。该系列专注于实现从智能办公到无人机领域(图 2)的多方位扩展。

图 2:作为 RZ/V 系列的中端产品,RZ/V2N 可支持家庭用移动机器人和驾驶员监测系统等应用。(图片来源:Renesas Electronics Corporation)

图 2:作为 RZ/V 系列的中端产品,RZ/V2N 可支持家庭用移动机器人和驾驶员监测系统等应用。(图片来源:Renesas Electronics Corporation)

视觉 AI 微处理器的要求

边缘 AI 应用通常在嵌入式设备上运行,这些设备可能采用电池供电或在低功耗状态下运行。因此,要求视觉 MPU 不仅具有强大的推理功能,还具有远少于传统高性能计算设备的能耗。

理想的视觉 AI MPU 在性能、能效、集成度、开发便捷性和安全性之间达到了完美的平衡。选择 MPU 时需要考虑的一些关键特性如下:

- 推理能力:RZ/V2N 通过其 DRP-AI3 集成加速器,可实现最高 15 TOPS 的性能,使其适用于智能摄像头、工业检测和边缘机器人等中端应用。虽然如协作机器人和自主无人机等一些高性能系统,可能需要 80 到 100 TOPS,但许多边缘 AI 应用在 1 到 15 TOPS 的性能下也能很好地运行,具体取决于其复杂程度。每瓦 TOPS (TOPS/W) 定义了产品的效率,即每瓦每秒条件下能够执行的运行次数。

尽管 TOPS 提供了性能的基准指标,但通过引入专用 AI 加速器可以显著提升实际推理速度。这种加速器能够卸载依赖密集型矩阵和张量计算的视觉 AI 工作负载。这使得系统能够更快、更高效地运行,同时减少时钟周期,降低功耗。

- 低功耗运行:许多边缘设备由电池供电或在严格的温度限制条件下运行。专为边缘 AI 设计的视觉 MPU 通常集成了动态电压和频率调节 (DVFS) 技术,这项技术可根据工作负载需求动态地调整功耗。结合可压缩模型规模并减少冗余计算的神经网络剪枝等技术,DVFS 有助于实现更高的 TOPS/W 值,从而提升运行效率,延长电池续航时间。DRP-AI3 加速器有助于避免使用高功耗 GPU,从而在边缘实现更高的 TOPS/W 值。

- 片上图像处理:配备可选内置图像信号处理器 (ISP) 的视觉微处理器,可执行常规图像处理任务,包括黑电平校正、色彩校正、裁剪及阴影校正。在安全或监控应用中,ISP 还可以对数据帧进行预过滤。例如,在连续视频流中,系统可能会丢弃静止帧,仅将包含运动或活动(如入侵检测)的帧发送至 AI 处理器,从而减少不必要的推理并节省功耗。

- 片上存储器:存储器也是影响性能和效率的重要因素。将数据保存在本地可以避免访问外部存储器时产生延迟和能耗,尤其是在实时 AI 推理过程中,这些是非常显著的影响因素。凭借 1.5 MB 的片上 SRAM 和对 LPDDR4X 存储器的支持,RZ/V2N 在内部处理速度与可扩展存储器选项之间实现了平衡。

- 加速 AI 部署:包含预编程应用和接口的人工智能工具包和评估板,有助于开发人员进行快速原型设计,部署视觉 AI 应用。此外,MPU 还应支持标准的 AI 模型格式。RZ/V2N 兼容标准模型格式,例如 ONNX 和 TensorFlow Lite。

- 安全:在边缘环境中,每个传感器或端点都可能成为潜在的攻击入口。因此,视觉 MPU 必须能够支持内置安全功能,例如安全启动和数据路径加密。RZ/V2N 支持安全启动和硬件级加密功能,并采用 Arm TrustZone 技术实现可靠的运行隔离,从而有效保护模型完整性和敏感性输入数据的安全。

RZ/V2N MPU 的 AI 设计人性化特性

Renesas 的专有 AI 加速器 DRP-AI3(动态可重构处理器)的 TOPS/W 值为 10,而且可通过先进的剪枝技术进一步提升至 15 TOPS/W。该技术会压缩系统须处理的模型规模。这样,就无需采用独立图形处理单元 (GPU) 或现场可编程门阵列 (FPGA)。

RZ/V2N 的大小仅为 15 平方毫米,使其成为紧凑型设备的理想之选。将四核处理器、专用 AI 加速器和双摄像头输入支持功能整合到一个设备中,为设计人员在智能摄像头、安全设备、机器人乃至消费类家电等应用中集成视觉 AI 技术带来了全新机遇。

MPU 采用低功耗设计,从而减少了发热,无需增加散热系统和风扇,因此缩小了嵌入式系统的体积并降低了成本。凭借支持双摄像头的能力,该器件可在应用中实现双视角成像,并提升空间识别能力。一个系统可以执行多种任务,例如同时统计停车场内的车辆数并识别车牌。

RZ/V2N 处理器架构

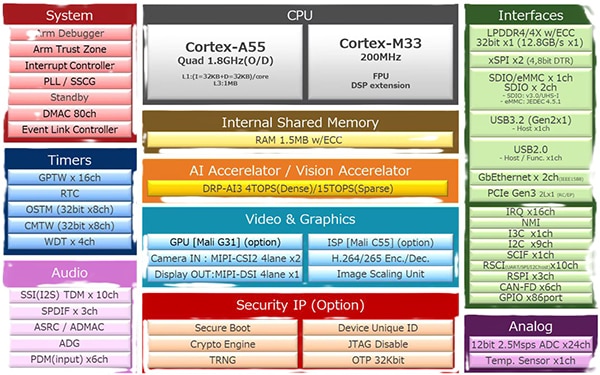

RZ/V2N MPU 提供了一系列全面的功能和特性,专为开发需要高性能 AI 且价格实惠的中端 AI 市场应用而设计(图 3)。

图 3:RZ/V2N 架构。( 图片来源:Renesas Electronics Corp.)

图 3:RZ/V2N 架构。( 图片来源:Renesas Electronics Corp.)

其中一些特性包括:

- 中央处理器 (CPU):该混合架构采用 Cortex-A55 四核 1.8 GHz 高性能CPU,以及专为实时控制和安全相关任务设计的低功耗 Cortex-M33 200 MHz 核心。

- 内部共享存储器:1.5 MB RAM,用于带错误校正码 (ECC) 的片上存储器,有助于确保数据完整性。ECC 算法能够检测并纠正数据在存储和传输过程中出现的错误。1.5 MB 片上存储器使 AI 算法能够快速运行,而 RZ/V2N 还配备了外部 DDR 存储器接口,方便在需要更多存储器时进行扩展。

- AI 加速器:Renesas 的 DRP-A13 专用 AI 引擎可执行高速 AI 推理任务,满足终端设备对低功耗和灵活性的需求。

- 视频和图形:可选的图形处理单元 (GPU) 和图像信号处理器 (ISP),有助于更高效地处理图像和渲染图形。

- 计时器:计时器支持实时操作,这对电机控制和其他自动化应用至关重要。

- 音频模块: 适用于多声道音频应用,如智能音箱和车载娱乐系统。

- 接口:高速存储器接口和高带宽外设是可以连接至视觉微处理器模块的众多接口中的一部分。

- 模拟模块:一个 12 位模数转换器 (ADC),无需在控制系统或监控应用中使用独立的 ADC。

Renesas 还为 RZ/V2N 提供了 RTK0EF0186C03000BJ 评估板套件,使设计人员能够快速地进行原型设计,评估视觉 AI 应用(图 4)。借助该公司提供的 AI 应用和 AI SDK,设计人员还可以在 GitHub 上访问涵盖超过 50 个用例的 AI 应用。

图 4:RZ/V2N 评估板套件包含主板、扩展板、两块子板以及 AI SDK。(图片来源:Renesas Electronics Corp.)

结语

Renesas 的 RZ/V2N 处理器是中端边缘 AI 应用的理想选择,能够以高速度、低延迟的方式提供数据驱动型信息。紧凑的外形和在低功耗运行时满足推理需求的能力,使其适用于各种嵌入式设备。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。