如何使用熟悉的工具在 FPGA 上部署边缘 AI

投稿人:DigiKey 北美编辑

2026-02-17

网络边缘的AI(边缘 AI)很少仅仅意味着推理。现实世界的部署通常涉及高速输入/输出 (I/O)、信号调节和实时控制回路,所有这些都是并发执行的。这些多功能工作负载要求紧密协调和高度确定性,而设计人员发现使用主流 AI 硬件难以满足这些要求。

两个因素使得这个问题变得更加复杂。首先,AI 模型正以惊人的速度发展,促使设计人员采用支持快速算法更新的平台。同时,许多边缘系统在现场使用的时间长达十年或更长,因此很难确保长期适应性。其次,从训练有素的模型到系统部署落地的路径仍然支离破碎。数据科学家使用 PyTorch 和 TensorFlow,而嵌入式团队则使用完全不同的工具链,这就造成了交接过程中的摩擦,从而拖慢了投产速度。

要应对这些挑战,就需要平台能够将高吞吐量 AI 处理与确定性行为、灵活的 I/O 以及长期适应性结合起来,所有这些都必须在有限的边缘部署典型功耗范围内实现。

本文重点介绍了那些挑战设计人员探索新型边缘 AI 架构的应用场景及其相关要求。然后介绍了 Altera 提供的支持边缘 AI 的现场可编程门阵列 (FPGA) 器件和软件工具,并展示了如何利用它们来满足这些应用在广泛性能和功率点上的需求。

边缘 AI 的演进需要架构创新

边缘系统越来越多地采用多样化的 AI 技术,包括用于异常检测的经典机器学习 (ML)、用于感知的卷积神经网络 (CNN) 以及用于大语言模型 (LLM) 的转换器。这些计算密集型算法通常与苛刻的非 AI 功能共存,例如信号处理、网络通信和实时控制。

自主系统就是一个很好的例子。它们通常需要从多种传感器模态(例如视频、音频、雷达、激光雷达和运动/位置反馈)摄取数据,以高吞吐量预处理这些数据流,使用复杂的 AI 分析结果,然后管理高精度控制环路,所有这些都需要可靠的确定性。

类似的例子在工业自动化、医疗成像、国防和电信应用中还有很多。它们面临的一个共同的难题是,传统架构难以适应不断融合的工作负载。

FPGA 为何特别适合边缘 AI

相比之下,这些要求与 FPGA 的功能完全吻合。FPGA 的核心是提供可配置的逻辑,以真正的并行方式执行操作,其时序行为在设计时就已植入,而不是在运行时波动。这种架构可实现对边缘 AI 至关重要的低延迟确定性。灵活的逻辑还可利用强大的 I/O:FPGA 通常提供丰富的高速 I/O,可与各种传感器和执行器连接,实现与 AI 处理的紧密耦合。

FPGA 还包含分布式内部存储器,可使数据靠近对其进行操作的逻辑。这就减少了多个处理阶段必须竞争访问共享存储器总线时出现的瓶颈,而这正是基于处理器的架构中常见的限制。

许多 FPGA 还集成了专门的数字信号处理 (DSP) 硬件。与通用结构相比,这些强化电路为信号处理工作负载提供了更高的性能和更好的能效。一些 FPGA 还集成了可运行标准软件栈(包括 Linux)的硬连线处理器系统,从而能够为网络、设备管理和用户界面等任务进行传统软件开发。

简而言之,单个 FPGA 就能整合原本可能需要单独的 I/O 芯片、AI 加速器、DSP 和控制平面处理器才能实现的功能。这样可以减少物料清单 (BOM),缩小电路板面积,降低功耗,同时保持边缘 AI 应用所需的低延迟和确定性。

AI 张量块的加入如何开启新的可能性

传统的 FPGA DSP 硬件已经非常适合许多边缘工作负载,但 AI 推理往往以密集但低精度的乘积运算为主。为了解决这个问题,Altera 的 Agilex 3 和 Agilex 5 器件采用了带有 AI 张量块的增强型 DSP。这是矩阵-矩阵和向量-矩阵乘法的专用硬件,在 AI 计算图中反复出现。

这种方法的核心是标量积和加法器/累加器引擎(图 1)。在张量模式下,硬连线点引擎使用 8 位输入和预加载的 8 位权重执行 10 元素点积。为了扩展动态范围,数据路径还可以使用共用的“公共指数”进行块浮点式缩放,以应对 AI 推理通常需要高动态范围但低精度的典型场景。

图 1:AI 张量块可以执行 10 元素点积。(图片来源:Altera)

图 1:AI 张量块可以执行 10 元素点积。(图片来源:Altera)

点积结果为 32 位(定点或单精度浮点),可以级联到附加加法器/累加器级,以跨相邻块计算更大的点积。每个 AI 张量块包括两个点积列,可实现多种运行模式。

在典型的使用案例中,一些增强型数学硬件被用于传统的 DSP 功能,例如对雷达数据执行快速傅立叶变换 (FFT)。另一些则用作 AI 张量块,如用于物体检测的 CNN。这种灵活性对于必须在处理其他计算密集型功能的同时处理 AI 的边缘系统来说至关重要。

针对不同 AI 工作负载的系列 FPGA 选择

Agilex 系列在性能扩展方面也具有相当大的灵活性。器件范围从专注于效率、尺寸仅为 12 mm × 12 mm 的器件,到提供高达 152.6 峰值每秒万亿次操作 (TOPS) 的高性能变体,同时在 I/O 和存储器接口能力方面也有类似的扩展。

Agilex 5 A5ED065BB32AE4SR0 就是高性能器件的一个实例,它采用 32 × 32 mm 封装,可提供 22.17 TOPS 的性能。以 Agilex 3 A3CW135BM16AE6S 为例,它在 16 × 16 mm 的封装中提供 2.8 TOPS 的性能。表 1 列出了每种器件的主要规格。

|

表 1:所示为 Agilex 5 和 Agilex 3 FPGA 样品的一些主要规格。(表格来源:Altera(经作者修改))

这两个系列既有传统的 FPGA,也有集成了 Arm 处理器的片上系统 (SoC)。Agilex 3 SoC 采用双核 800 兆赫 (MHz) Arm Cortex-A55。Agilex 5 SoC 采用双 1.8 千兆赫 (GHz) Cortex-A76 内核和双 1.5 GHz Cortex-A55 内核的非对称集群。这两种配置都支持 Linux,可用于网络、设备管理和用户界面的常规软件开发。

使用 FPGA 简化边缘 AI 部署

AI 模型通常是在以软件为中心的框架中开发的,迭代周期较快,而 FPGA 实现历来需要硬件开发技能和较长的集成周期。Altera 的 FPGA AI 套件(图 2)采用与行业标准 AI 工具兼容的流程,提供了从训练有素的模型到可部署 FPGA 推理知识产权 (IP) 的更直接途径。

图 2:FPGA AI 套件工作流是标准 AI 框架与 FPGA 部署之间的桥梁。(图片来源:Altera)

图 2:FPGA AI 套件工作流是标准 AI 框架与 FPGA 部署之间的桥梁。(图片来源:Altera)

该工作流汇总如下:

- 在 PyTorch、TensorFlow 或 ONNX 等标准框架中开发推理模型。

- 使用 OpenVINO 工具包将模型转换为由图形文件 (.xml) 和权重 (.bin) 组成的中间表示 (IR)。

- 将 IR 文件传入 FPGA AI 图形编译器,该编译器会将模型映射到可用的 FPGA 资源上。这些资源可包括外部主机处理器、内部处理器或无头配置。

- 使用 Quartus Prime 专业版编译和部署生成的层,通过推理引擎运行时栈和 FPGA AI 应用编程接口 (API) 管理存储器移动和硬件调度的执行。

- 作为编译过程的一部分,使用架构优化器来平衡性能和资源使用。例如,利用它来确保实现符合推理吞吐量目标,同时为其他 FPGA 逻辑留出空间。

实际上,这种方法的价值在于,它将“在 FPGA 上部署”变成了一个集成过程,而不是加速器设计工作。数据科学家可以保持既定的模型开发工作流,而 FPGA 和嵌入式团队收到的 IR 文件可以自然地融入构建和部署周期,从而随着模型和需求的发展实现更快的迭代。通过 Open Model Zoo for OpenVINO 工具包提供的预训练模型可以进一步加快开发速度。

使用简单易用的开发套件快速入门

要开始在 FPGA 上探索边缘 AI,设计人员有多种开发套件可供选择。对于更高性能的应用,Terasic P0775 Atum A5 开发套件(图 3)就是一个不错的选择。该套件以 Agilex 5 A5ED065BB32AE4SR0 为核心,提供适合边缘级系统的各种接口。主要特性包括 8 千兆字节 (Gb) DDR4、QSFP+ 和 2.5 千兆位 (Gb) 以太网 (GbE) 端口、PCIe Gen 3 x4、双 MIPI 摄像头连接器和 HDMI 输出。该套件包括 Quartus Prime 专业版的免费许可。

图 3:P0775 Atum A5 开发套件可用于高性能 AI 和视觉开发。(图片来源:Terasic)

图 3:P0775 Atum A5 开发套件可用于高性能 AI 和视觉开发。(图片来源:Terasic)

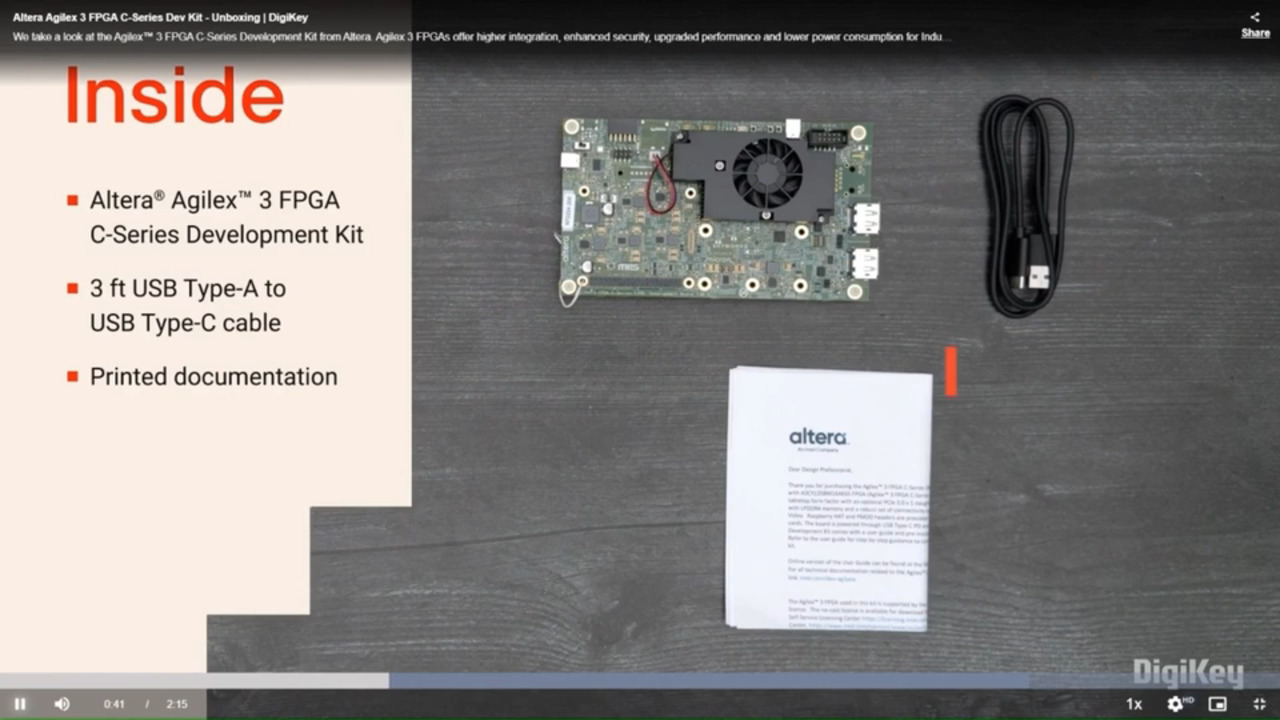

对于注重效率的应用,设计人员可以采用 DK-A3W135BM16AEA Agilex 3 FPGA 和 SoC C 系列开发套件(图 4)。该套件围绕 Agilex 5 A5ED065BB32AE4SR0 构建,提供了适合边缘级系统的广泛接口组合。该开发板提供 4 Gb LPDDR4、GbE、DisplayPort 和 USB 2.0,以及一个 Raspberry Pi HAT 连接器和一个用于低摩擦扩展的 Digilent Pmod 接口。

图 4:DK-A3W135BM16AEA Agilex 3 FPGA 和 SoC C 系列开发套件为注重效率的边缘 AI 提供了一个紧凑型平台。(图片来源:Altera)

图 4:DK-A3W135BM16AEA Agilex 3 FPGA 和 SoC C 系列开发套件为注重效率的边缘 AI 提供了一个紧凑型平台。(图片来源:Altera)

结语

LLM 和其他新型 AI 工作负载在边缘的引入正在促使开发人员寻求新的方法。FPGA 提供了一种独特的解决方案,不仅带来了低延迟和性能确定性,还能处理许多其他系统功能。借助支持 AI 的 Agilex FPGA 和 FPGA AI 套件,开发人员可以快速轻松获取这些能力,为高度自适应、长寿命的设计开辟了新的架构可能性。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。