特性

以下主题通过 Lattice Diamond 2.0.1 版设计软件展开。

• Lattice Diamond 设计流程工具基础概述

• 在顶层层次结构中实例化 VHDL 模块

• 使用 Diamond 设计视图生成层次结构

• 使用 Diamond 设计视图生成测试平台模板

• 使用自定义测试平台创建 Active-HDL 项目

• 在 Active-HDL 中查看信号并运行自定义测试平台

简介

本教程将介绍基于 Lattice Diamond 2.0.1 版本和 Active-HDL 软件,针对 Lattice LFE2-70E FPGA 进行基础测试平台创建与仿真的方法。该测试平台将为组合逻辑超前进位加法器提供激励信号,该加法器的详细实现可参阅另一篇 eeWiki 技术文章。VHDL 模块已提供,用户只需创建原理图符号、顶层原理图文件以及用于 Active HDL 的测试平台模板。

背景知识

Lattice ECP2 是中密度器件(6至95K LUT,90至583 IO),具备 sysDSP 和灵活内存资源。可支持3至42个高性能DSP模块,以及55Kbits至5308Kbits的sysMEM嵌入式块RAM。本教程基于仿真,仅需软件操作。

所需软件:

• Lattice Diamond 2.0.1设计软件(含第三方软件Synplify Pro for Lattice)• Active-HDL Lattice Edition

应用场景

电路构建

-

开发第一步是启动Lattice Diamond设计软件,通过新建项目向导创建项目。文件(File) → 新建(New) → 项目(Project)。输入项目名称(如Testbench_Tutorial)和存储路径。

-

点击"下一步(Next)>"进入添加源文件窗口。点击"添加源文件(Add Source)“导入eeWiki网页为本项目提供的VHDL模块。添加Top_Testbench_Tutorial.vhd、dflipflop_nbit.vhd和nbitsatadder.vhd文件,并勾选"复制源文件到实施目录”(Copy source to implementation directory)。

-

点击"下一步(Next)>“进入器件选择窗口(Select Device Window)。按以下参数设置后点击"下一步(Next)>”:

• 系列: LatticeECP2

• 器件: LFE2-70E

• 性能等级: 5

• 封装类型: FPBGA672

• 工作条件: 商用级

• 部件名称: LFE2-70E-5F672C -

确保设置正确后点击“完成(Finish)>”。其他LatticeFPGA也可遵循相同流程,仅需在器件选择窗口中调整不同设置。

-

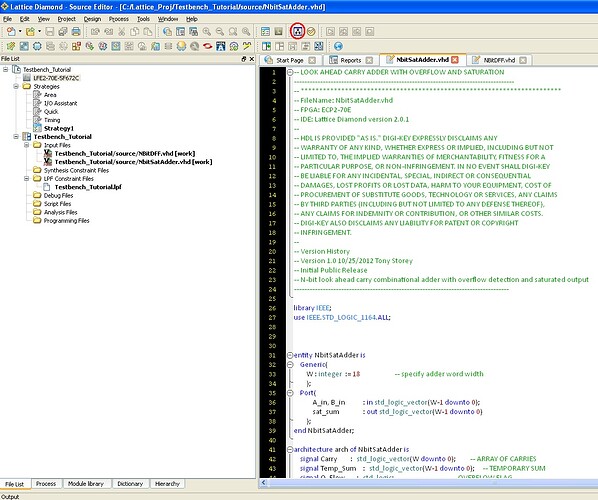

在文件列表窗口中双击任意.vhd文件即可打开查看。界面应类似于下方图1所示。

图 1 - Diamond 设计环境

-

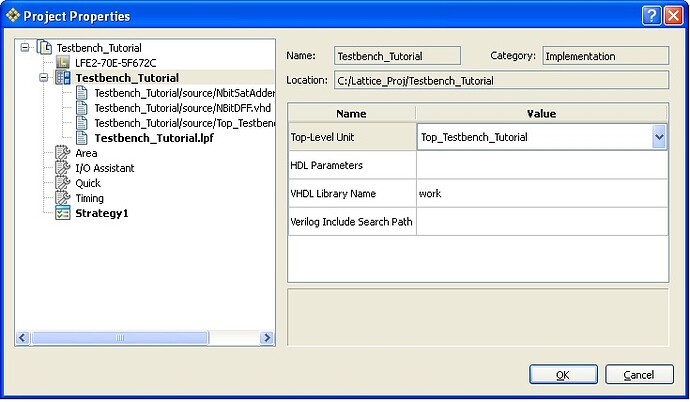

在文件列表窗口(File List Window)中,右键点击输入文件文件夹上一级的活动实现文件夹,从弹出菜单中选择属性(Properties)。

-

在项目属性(Project Properties)对话框中,确保项目处于高亮状态,并在"顶层单元(Top-Level Unit)"的值单元格中选择Top_Testbench_Tutorial。此文件名可能需要手动输入。如图2所示。

图 2 - 项目属性窗口

-

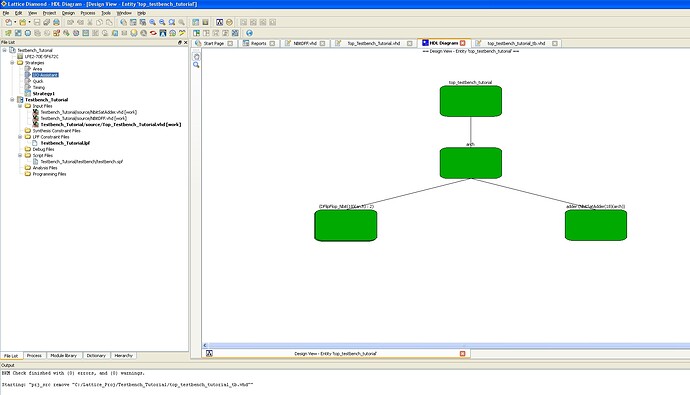

点击顶部工具栏的"生成层次结构(Generate Hierarchy)"按钮,或选择设计(Design)→生成层次结构(Generate Hierarchy)。

-

此时应看到设计视图(Design View)中按层次排列的VHDL组件。现在点击"运行BKM检查(Run BKM Check)"或选择设计(Design)→运行BKM检查(Run BKM Check)。VHDL模块应显示为绿色,表示(0)错误和(0)警告。如图3所示。

图 3 - 生成层次结构后的设计视图

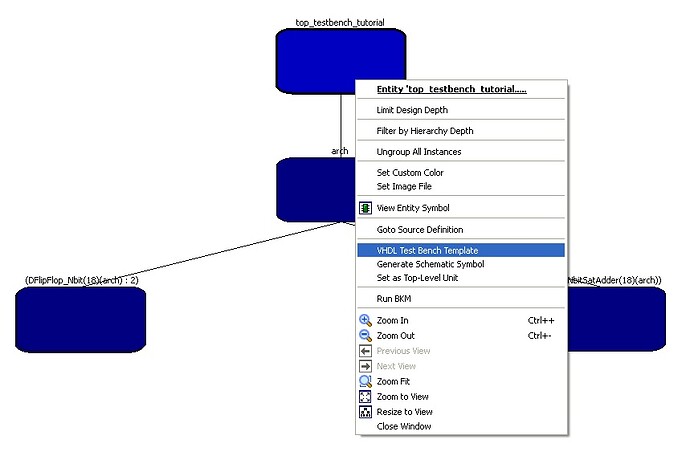

- 在设计视图(Design View)中右键点击top_testbench_tutorial,选择VHDL测试平台模板。如图4所示。

图 4 - 创建测试平台模板

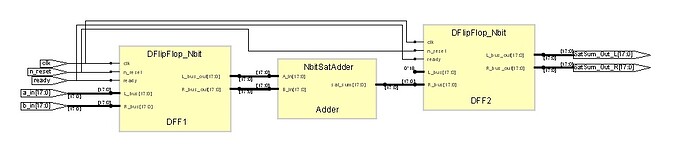

- 文件列表窗口(File List Window)的输入文件(Input Files)文件夹下将创建新文件。这是测试平台模板,包含运行仿真所需的大部分VHDL代码。文件可在此路径运行,也可移至源文件夹。现在可将测试平台从"testbench.vhd"重命名为"top_testbench_tutorial_tb.vhd"(本例采用此名称)。测试平台还需自定义测试向量驱动顶层设计输入端口,以及控制时钟的进程。需在"tb:PROCESS"进程中进行信号赋值。将添加名为“clock:PROCESS”的进程来控制时钟。可在Synplify Pro中(可选)创建驱动架构的RTL原理图,方法是在Lattice Diamond工具栏中打开Synplify Pro,运行设计后点击“RTL视图(RTL View)”按钮。这将生成如图5所示的RTL原理图。

图 5 – RTL 原理图

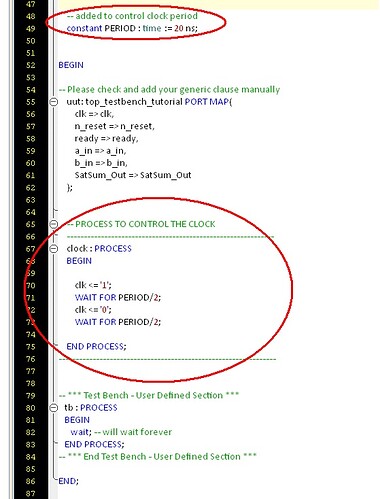

- 在“PORT MAP”上方的“BEGIN”语句之前插入以下内容:

• constant PERIOD : time := 20 ns;

在“tb:PROCESS”之前插入以下VHDL代码来控制时钟:

• clock : PROCESS

• BEGIN

•

• clk <= ‘1’;

• WAIT FOR PERIOD/2;

• clk <= ‘0’;

• WAIT FOR PERIOD/2;

•

• END PROCESS;

- 在“tb : PROCESS”中的BEGIN与wait语句之间输入以下VHDL代码以驱动输入端口:

• ready <= ‘0’;

• n_reset <= ‘0’;

• WAIT FOR 40 NS;

• n_reset <= ‘1’;

• WAIT FOR 40 NS;

• ready <= ‘1’;

• a_in <= “001100111111111111”;

• b_in <= “000010000000000001”;

• WAIT FOR 10 NS;

• a_in <= “101100111111111111”;

• b_in <= “100010000000000001”;

• WAIT FOR 10 NS;

• a_in <= “011100111111111111”;

• b_in <= “010010000110000001”;

• WAIT FOR 10 NS;

• a_in <= “101100000100001111”;

• b_in <= “100010000000000001”;

• WAIT FOR 10 NS;

• a_in <= “101111111111111111”;

• b_in <= “111110001111100001”;

• WAIT FOR 40 NS;

• a_in <= “111111000001111111”;

• b_in <= “111011111111100001”;

• WAIT FOR 40 NS;

• a_in <= “001111111111111111”;

• b_in <= “101001100011100001”;

• WAIT FOR 40 NS;

• a_in <= “001111110000110011”;

• b_in <= “001011111111100001”;

• WAIT FOR 40 NS;

• a_in <= “100000111111111111”;

• b_in <= “111101101111100001”;

• WAIT FOR 40 NS;

• a_in <= “000000000000001111”;

• b_in <= “011010000011100110”;

- 代码应按照图6和图7所示输入。

图 6 – 添加时钟进程后的修改版测试平台

图 7 – 添加测试向量后的修改版测试平台

-

保存设计,点击顶部工具栏的Simulation Wizard,或选择Tools → Simulation Wizard。

-

输入项目名称(本例中为“testbench”),并浏览至正确的项目位置。选择Active-HDL单选按钮,点击Next>。

-

选择RTL单选按钮,点击Next>。

-

在“Add and Reorder Source”窗口点击Next>。

-

在“Parse HDL files for simulation”窗口中,确认“top_testbench_tutorial_tb”设置为“Simulation Top Module:”,点击Next>。

-

在“Summary”窗口中,确保勾选“Run Simulator”后点击Finish。

-

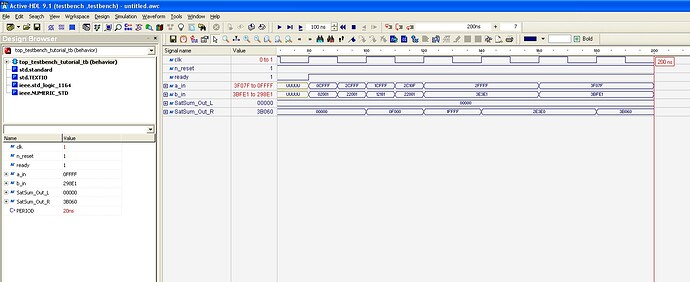

Active-HDL将启动;在“Files”窗口中展开“work library”,右键点击“top_testbench_tutorial_tb (behavior)”,选择Initialize Simulation。如图8所示。

图 8 – Active-HDL 仿真初始化

- “Structure”标签页将置顶,此时可将顶层端口添加至波形窗口。右键点击每个信号,从弹出菜单中选择Add to Waveform。如图9所示。

图 9 – 将端口信号添加至波形图

-

现在可通过点击工具栏中的“Run For”(F5)按钮,或在“Console”窗口中输入“run”加指定时间(如“run 100 ns”)来运行测试平台。

-

另一个实用命令是“restart”,该命令会从测试平台的开头重新启动仿真。测试平台仿真的最终结果应类似于下图10所示

图 10 – 测试平台最终结果

功能、限制与修改

本教程使用Lattice Diamond 2.0.1版本开发,并得到Synopsys(Synplify Pro for Lattice)和Aldec(Active-HDL Lattice Edition)配套软件支持。Diamond可作为独立开发环境,配合其他综合与仿真软件使用。

结论

本教程展示了如何轻松运用Lattice Diamond设计软件,基于模板创建自定义用户测试平台。只需遵循本教程所述步骤,即可为任何设计创建定制化测试平台。

附加信息

更多设计支持、产品教程、应用说明、用户指南及其他文档,请访问Lattice官网:https://www.latticesemi.com/zh-CN/Support 。

附录:文件下载

LD_Testbench_Tutorial.doc (774 KB)

Top_Testbench_Tutorial.vhd (3.1 KB)

NbitSatAdder.vhd (3.0 KB)

NBitDFF.vhd (2.0 KB)

top_testbench_tutorial_tb.vhd (3.9 KB)