特性

涵盖以下设计主题:

• 前瞻进位组合加法器与饱和数学运算的方法论及逻辑原理

• 利用生成语句通过结构性组合方式扩展逻辑切片

• 使用通用FPGA供应商原生工具集进行性能基准测试

• 通过测试平台对N位饱和数学前瞻进位组合加法器进行仿真

引言

该VHDL模块基于二进制前瞻进位加法器的基本布尔方程,采用结构化的方式构建这些方程。通过VHDL生成语句和通用变量,可按用户需求将逻辑切片扩展至目标字宽。

加法器的饱和运算部分确保在DSP及控制相关设计中实现无毛刺性能。该加法器通过检测溢出状态,将输出饱和为最大正满幅值或负满幅值。

开发采用Xilinx Spartan 6开发套件及ISE v13.1开发环境,但并不限定必须使用该工具集。可通过以下链接在DigiKey公司网站获取Xilinx、Microsemi、Lattice和Altera的多种开发套件。

背景

前瞻进位加法器通过评估相加的两个字,识别进位生成位与进位传播位。这些进位位将以组合方式确定所有可能产生进位的位置。当每个进位位可用时,加法运算以切片为单位同步完成。饱和状态由溢出标志位和临时和的最高有效位共同决定。

应用场景

电路构建

VHDL生成语句是构建每个切片布尔方程的理想解决方案。这能根据用户需求实现灵活扩展。VHDL模块采用通用变量确定加数字宽,生成语句据此构建结构逻辑。初始进位输入设为’0’,后续进位则取决于两个加数从最低有效位到最高有效位的各位。各切片组合构建的电路仅受门延迟限制,实现高速运算。基本进位前瞻加法器切片如图1所示。

图 1 基本进位前瞻加法器切片

饱和状态由溢出条件决定。该条件通过计算最高有效位的进位输入与进位输出的异或值来判定,这两个最高有效位位于进位阵列中。若发生溢出,临时和的最高有效位将决定最终和应饱和至最大正值还是最大负值。'1’表示溢出导致正值翻转为负值,因此我们将最终和值饱和为正值。'0’则表示相反情况,因此我们将最终和值饱和为负值。该加法器的三切片实现如图2所示。输出和饱和情况如图3所示。

图 2 支持 W 位加数宽度可选扩展的三切片实现

图 3 支持 W 位加数宽度可选扩展的三切片实现

基准测试

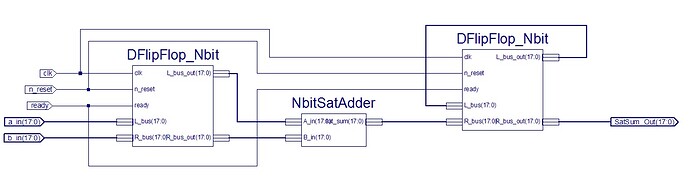

可通过将组合加法器置于两个n位时钟触发器之间进行基准测试。在加数字宽恒定的情况下,这将决定加法器的最高运行速度。64位版本在Spartan 6器件(-3速度等级)上实现了100MHz运行频率,每个结果生成时间小于10纳秒。设计约束为10纳秒,未进行额外优化。使用不同FPGA或同型号不同速度等级器件将获得不同结果。通过合理设置约束条件并优先优化速度而非面积,可利用FPGA供应商原生工具链进行优化。测试方案的顶层示意图见图4。

图 4 组合加法器基准测试顶层原理图

电路仿真

可采用ModelSim或Xilinx Isim等HDL仿真器验证电路输出。本设计采用Isim进行仿真。测试平台在Xilinx ISE v13.1开发环境中创建。测试平台包含两个进程:时钟进程与输入信号进程。输出结果可在下方图5中查看。红色与蓝色圆圈标明了因溢出条件导致输出饱和的位置。该设计的测试平台文件已包含在其他设计文件中。

图 5 Isim 测试平台输出

功能、限制与修改

本设计可适配任何FPGA开发平台,性能表现各异。随着字宽增大,硬件资源消耗量也会显著增加。本VHDL模块采用Xilinx ISE v13.1开发工具,基于Spartan 6开发平台进行开发和基准测试。使用Xilinx内置Isim仿真软件对设计进行仿真验证。

结论

NbitSatAdder.vhd文件可修改并实例化到任何需要高速运算和输出饱和特性的设计中。该模块在级联加法器电路(如并行FIR滤波器电路)中表现优异。在低速FPGA中使用时,采用N位时钟触发器能有效同步电路以满足时序要求。可通过以下链接在DigiKey公司网站获取Xilinx、Microsemi、Lattice和Altera的多种开发套件。

附加信息

更多设计支持、产品教程、应用笔记、用户指南等文档可从四大FPGA供应商官网获取:

Xilinx应用支持:https://xilinx-wiki.atlassian.net/wiki/spaces/A/overview

Microsemi SOC集团官网:https://www.microchip.com/en-us/products/fpgas-and-plds

Lattice官网:https://www.latticesemi.com/zh-CN

Altera技术支持:https://community.altera.com/category/forums

附录:下载资源

完整LookAheadCarryStaurationAdder.xise项目文件可在此下载。

NbitSatAdder.vhd (3.0 KB)

NBitDFF.vhd (1.9 KB)

Adder_test.vhd (3.3 KB)

Top_Level.sch (6.8 KB)