特性

以下主题通过Lattice Diamond 2.0.1版设计软件实现。

- FIFO缓冲模块概述及常见用途

- 水位标志实现方法

- FIFO配置

- FIFO缓冲模块测试平台

概述

该模块(提供Verilog和VHDL版本)是先进先出缓冲模块,常用于缓冲变速率数据传输或暂存数字通信与信号处理算法中的数据。例如,FIFO模块可用作FIR滤波器中的环形缓冲区或延迟线。

若条件允许,工具将自动调用FPGA内嵌的块RAM资源。FIFO.vhd和FIFO_v.v模块通过测试平台验证,在向FIFO读写数据时同步监测RAM数据及输出标志状态。

背景知识

本FIFO模块为可变长度缓冲器,支持可调节的寄存器字宽与地址空间(即深度)。提供"将满"和"将空"状态的水位标志。"将满"与"将空"标志的触发深度可通过模块参数化设置调整(VHDL版本通过generic块实现)。FIFO还包含空、满及错误状态标志。设有数据计数输出端口。如端口名称所示,该端口向模块外部显示当前读写指针之间存储的数据量。

本设计所需软件:

Lattice Diamond 2.0.1设计软件(需配合第三方软件Synplify Pro for Lattice及Active-HDL Lattice版使用)。

应用场景

电路构建

FIFO_v.v和FIFO.vhd可通过分别修改各模块内的参数化值和通用参数进行配置。输出字宽和FIFO地址空间均可按需缩放。通过调整ALMST_F和ALMST_E参数值,可设置水位标记在不同深度触发。

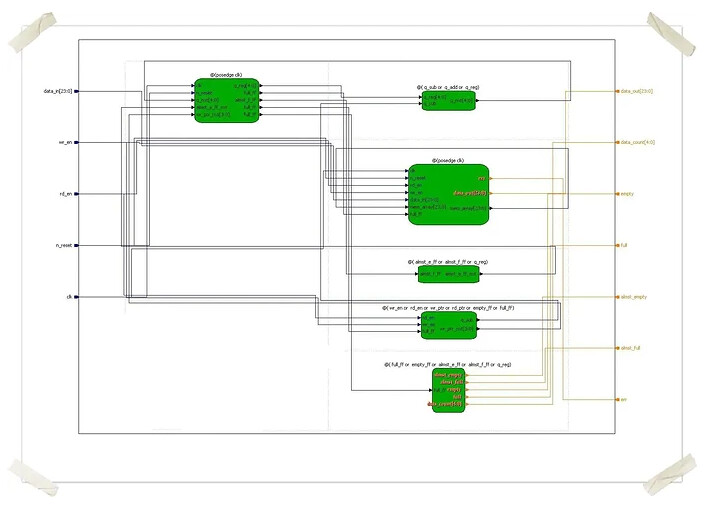

该设计包含数据输入端口、时钟、低电平有效复位、读使能、写使能、数据输出端口、数据计数端口、空标志、满标志、几乎空标志、几乎满标志及错误信号。下方图1展示了带有输入输出的VHDL生成黑盒模型。

图 1 - FIFO 缓冲器黑盒示意图

图2展示了通过Lattice Diamond"生成层级"功能得到的FIFO Verilog实现HDL框图。

图 2 - FIFO 模块框图

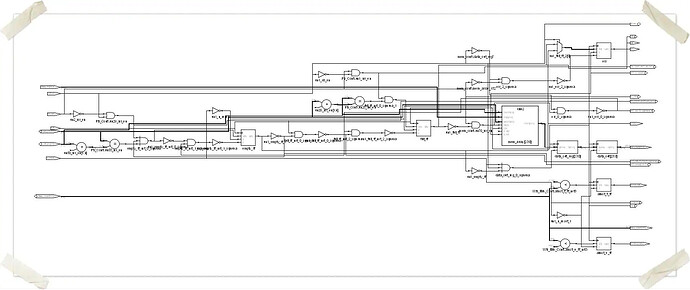

基础过程块(VHDL实现中称为process块)用于推导组合逻辑,通过控制指针和标志将推导出的RAM块构建为FIFO。VHDL和Verilog设计中共用的通用模块如下:

- 触发器更新,上升沿时钟敏感

- 几乎满/空标志控制,组合逻辑

- 读写指针控制,组合逻辑

- 存储器阵列读写控制,上升沿时钟敏感

- 带控制标志的计数器,组合控制

- 输出寄存器连接

图3展示了一个24位数据、4位地址空间,带有4字深"几乎满"和"几乎空"标志的RTL示意图。

图 3 - FIFO 缓冲器 RTL 示意图

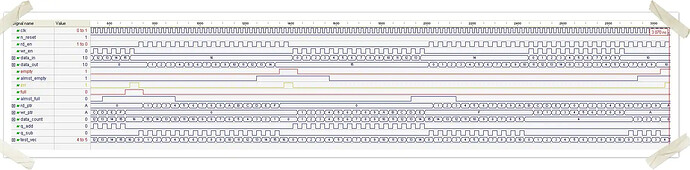

图4展示了带有测试向量的Aldec Active HDL测试平台输出。当FIFO接近空或满状态时,可调水位标记会先变高,随后相应的空或满标志生效。若在FIFO满时尝试写入,或空时尝试读取,错误标志将置高。

图 4 - FIFO Aldec Active HDL 测试平台输出

随附的测试平台通过"HDL图表"窗口中的"生成测试平台模板"命令创建。测试平台经修改后包含多种测试用例,用于验证条件标志并确保读写指针控制正确。提供的测试平台应涵盖大多数测试场景。

设计软件

使用Lattice Diamond 2.0.1版本开发了"FIFO.vhd"和"FIFO_v.v",并配合Synopsys(适用于Lattice的Synplify Pro)和Aldec(Active-HDL Lattice版)的支持软件。Diamond可作为独立开发环境,搭配其他综合与仿真软件使用。

结论

本设计展示了在Lattice Diamond设计软件中使用可配置FIFO模块的Verilog和VHDL实现。Verilog和VHDL测试平台演示了如何使用"for循环"生成测试向量和信号延迟。

附加信息

更多设计支持、产品教程、应用说明、用户指南及其他文档可在Lattice官网查阅:https://www.latticesemi.com/Support.aspx?source=topnav 。

附录

Verilog 文件:

FIFO_v.v (7.6 KB)

FIFO_v_tf.v (3.0 KB)

VHDL Files:

FIFO.vhd (8.1 KB)

fifo_tb.vhd (4.6 KB)