代码下载

FIR滤波器(顶层文件): fir_filter.vhd (3.3 KB)

数据类型(必须包含在项目中): types.vhd (1.8 KB)

特性

- FIR滤波器组件的VHDL源代码

- 可配置的数据输入位宽

- 可配置的系数输入位宽

- 可配置的抽头数量

概述

本文详述了用VHDL编写、适用于FPGA的FIR滤波器电路。该组件通过并行接口从用户逻辑读取数据流和滤波系数,并输出滤波结果。设计使用Quartus Prime 17.0.0版本完成。资源需求取决于具体实现方式。图1展示了集成到系统中的FIR滤波器典型实例。

图 1. 应用实例

背景知识

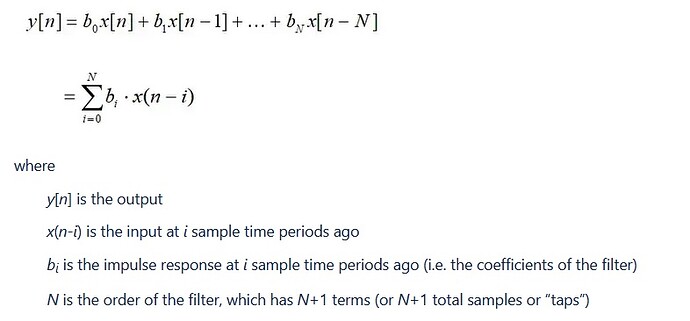

有限脉冲响应(FIR)滤波器的脉冲响应会在有限时间内衰减至零。它们具有固有稳定性,且无需反馈机制。

离散时间数字实现的输出是最近输入样本的加权和。其数学定义由卷积计算给出:

工作原理

FIR滤波器采用图2所示架构实现上述卷积函数运算。它会读取当前输入值(通过数据端口输入)及前N 个历史值(共N +1个抽头)。这些数值在每个系统时钟周期被移入,并通过数据流水线逐级移位。

FIR滤波器还会同步存储系数端口阵列输入的系数。这些系数决定了滤波器对各数据样本的加权比重。

每个系数都会与对应的数据样本相乘。滤波器将所有乘积结果相加,生成最终输出值。

图 2. 架构说明

FIR 滤波器配置

通过设置types.vhd文件中的常量参数来配置 FIR 滤波 器。表1列出了各参数说明。这些常量用于定义构成端口、内部流水线和内部数组的数据类型。

表 1. 常量描述

端口描述

表2描述了FIR滤波器的端口定义。

表 2. 端口描述

复位

reset_n 输入端口必须保持逻辑高电平,FIR滤波器组件才能正常工作。该端口低电平时将异步复位组件。复位期间,该组件会清空内部寄存器及输出结果端口。在reset_n 端口恢复高电平前,所有输入端口信号均被忽略。复位解除后,FIR滤波器立即恢复运行。由于内部数据流水线被清空,初始输出不会包含所有FIR滤波项,直到有足够的输入样本移入填满流水线。

结论

该FIR滤波器是可编程逻辑组件,执行离散卷积运算。输入数据大小、系数大小以及滤波器的抽头数量均可配置。