代码下载

ram.vhd (2.4 KB)

特性

- 单端口RAM组件的VHDL源代码

- 可配置的内存大小

- 可配置的每个数据字宽度

- 可综合成大多数FPGA的内部存储器块资源

简介

本文详述了一个用VHDL编写的单端口RAM电路。该内存组件从指定内存地址输出数据,并在写使能有效时将输入数据写入该地址。其设计采用Quartus Prime 17.0.0版本完成。资源需求取决于具体实现方案。图1展示了该RAM集成到系统中的典型示例。

图 1. 实现示例

架构

该RAM采用写前读架构。在写周期中,RAM会先写入数据再通过输出端口读取,因此输出端口显示的是正在写入的新数据,而非将被覆盖的旧数据。

配置 RAM

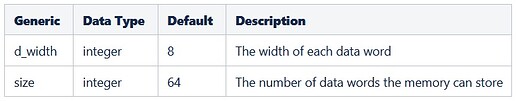

通过设置ENTITY中的GENERIC参数来配置RAM。表1描述了相关参数。

表 1. 通用参数说明

端口描述

表2描述了该RAM的端口。

表 2. 端口描述

结论

该可编程逻辑RAM是一个简单的单端口存储组件,它能从指定内存地址输出数据,并在写使能有效时将输入数据写入该地址。存储单元数量与数据宽度均可配置。