RISC-V 推出支持 AI 和 ML 的双核 64 位机器视觉/听觉开发板

32 位内核创新异军突起,RISC-V 新近加入。但这次是一个不同的工程环境。最近的内核创新和竞争主要集中在既有的通用微控制器市场,通用外设集中在恶劣的汽车应用方面。然而,今天的嵌入式领域则集中在物联网 (IoT) 终端,目标是复杂的工业边缘计算系统。最新的 RISC-V 微控制器不仅仅是通用的定时器和串行接口,还支持复杂的外设,包括人工智能 (AI) 推理引擎和机器学习 (ML) 功能。

但是 RISC-V 还有更多的优势,超出了不断发展的市场和技术的需求。在我们讨论这些之前,让我们快速了解一下来龙去脉。

微控制器创新简史

嵌入式微控制器市场每隔几年就会发生一次革命。具体发生时间不固定,这是因市场对性能和功能的需求所驱动的,也是因该行业的商业因素所决定的。从古老的 8051 开始,8 位市场几乎主导了所有的嵌入式系统,包括汽车、游戏和电器;直到今天,8 位超低功率微控制器仍然随处可见,甚至 8051 也还在继续创造着令人印象深刻的记录(后面会有更多介绍)。

而 16 位微控制器长期以来一直兼具低功耗和性能的优势,但直到今天,它仍然是一个被误解的市场,被许多老牌企业之外的厂家所误解。然后是 32 位处理器。在 20 世纪 90 年代和 21 世纪初的内核大战中,这些处理器在个人电脑之外的各种专有架构中变得非常重要。

Arm 让 32 位内核之争尘埃落定。各大厂商都松散地联合在一个共同的架构下,客户成为赢家,因为他们能够轻松地更换供应商,而不必为移植他们的代码付出巨大的努力,这是对专有架构的优势。

RISC-V 真正精减了指令集

在很长一段时间里,RISC-V 在市场份额方面几乎可以忽略不计,主要是因为市场对一个全新 32 位指令集架构 (ISA) 几乎没有什么需求。然而,任何看了 RISC-V 核心架构的工程师都会立即留下深刻印象。

在历史上 RISC 就是精减指令集内核/计算机的代名词,字面意思是它只有那些执行有用操作所需的最少指令。从早期开始,大多数现在被称为 RISC 的架构已经偏离了这个定义,有了许多复杂的指令,以至于工程师们现在对这个标签有一些嘲讽的态度。但是 RISC-V ISA 是真正忠实于这个定义的,绝对对得起 James Earl Jones 对这个架构给出的“厉害,太厉害了”的评价。

基本型 32 位 RISC-V 有 32 个 32 位心核寄存器,x0 到 x31。其中 31 个是通用的,而寄存器 x0 则硬接线到零。随着你对 RISC-V 指令集的深入研究,就可以明白 x0=0 的智慧,以及为什么 x0 是许多指令的必要操作数,就是保持精减指令集,对,就是精减。但这又是另一个故事了。

半导体行业是一个全球性的行业,有许多健康的依存关系,但现在的半导体供应商,出于某些明显而微妙的原因,希望对其产品保持更多的控制,这包括重新审视昂贵的许可协议和正在出售和转售的知识产权 (IP) 来源。这使得 RISC-V 成为一个可定制的、开源的、免版税的 ISA(指令集架构),是历史在正确的时间给我们提供的正确的架构。因此,DigiKey 在其教育网站上推出了 RISC-V 电子书《学术组件参考指南:RISC-V》,向新手和经验丰富的开发人员介绍 RISC-V 工具和评估套件。使用这些工具,之前没有架构经验的开发者也可以迅速熟悉和掌握 RISC-V 编程模型和 ISA。

RISC-V:强大的 AI/ML 内核

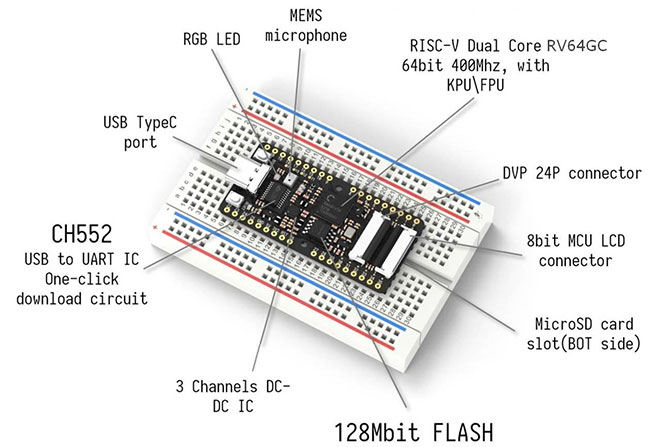

通常情况下,一个新的 ISA 会首先作为通用微控制器进入市场,并配有一个带有漂亮的闪烁 LED 的评估板,而 RISC-V 则直接进入了人工智能 (AI) 和机器学习 (ML)。例如,Seeed Technology 正在用基于 RISC-V RV64I 的 Seeed 110991190 Sipeed Maix-BiT 开发板来实现 ML,这是一个具有 64 位内核寄存器 x0 至 x31 的 64 位地址和数据 ISA(图 1)。

图 1:Seeed Technology Sipeed Maix-BiT 开发板基于双核 RISC-V RV64GC,目标是机器视觉和机器学习应用。(图片来源:Seeed Technology)

图 1:Seeed Technology Sipeed Maix-BiT 开发板基于双核 RISC-V RV64GC,目标是机器视觉和机器学习应用。(图片来源:Seeed Technology)

正如 DigiKey 的 RISC-V 电子书(从第 5 页开始)中所讨论的那样,该开发板尺寸小、性能高,因此适合边缘处理物联网应用。

Sipeed Maix-BiT 板的核心处理器是双核 RV64GC 微控制器系统级芯片 (SoC),其中G-suffix 指定支持硬件乘法和除法的通用扩展,原子式读改写内存指令,并支持单精度和双精度浮点。C 后缀表示微控制器支持 16 位压缩指令,对编写紧凑的代码很有用。该微控制器可以访问 6 兆字节 (MiB) 通用片上 SRAM,此外还有 128 兆位 (Mb) 的外部程序闪存。对于一个相对较新的 ISA 来说,这种处理能力令人印象深刻,对于复杂的边缘计算应用来说,存储空间也是足够。

这款 双核 RV64GC 微控制器最厉害之处是一个片上通用人工智能神经网络处理器,旨在用于实时人脸和物体检测。这种 AI 处理器有 2 MiB 专用 SRAM,用于执行 AI 操作。这种处理能力令人印象深刻,具有中等微控制器编程技能的人都可以使用。

Sipeed Maix-BiT 板包括一个用于闪存扩展的微型 SD 卡插槽。一个板载的微机电系统 (MEMS) 麦克风可与人工智能单元一起用于机器听觉应用,包括复杂的语音和噪音识别系统。该套件还包括一个外部摄像头,可插入电路板底部的数字视频端口 (DVP) 摄像头连接器。这有利于复杂的机器视觉应用,这是物联网边缘处理系统的一个优势。

该板还有一个用于编程和调试的 USB-C 接口,它通过一个 USB-UART 芯片与双核 RV64GC 对接。另外还有一个额外的连接器用于连接附带的外部 LCD 显示屏。这可以在程序开发过程中提供视觉反馈,也可以在应用中用于用户反馈。

结语

从 8 位微控制器的时代开始,微控制器经历了一个漫长的旅程。RISC-V ISA 能否在良性竞争的市场中与 Arm 并驾齐驱?随着人们对 RISC-V 和先进的开发板的兴趣,似乎可以肯定 RISC-V 有足够的动力将其带入市场,但这是一个更大的讨论主题。现在,随着 Seeed 的 110991190 Sipeed Maix-BiT 等产品的推出,它似乎肯定会在物联网和 AI/ML 边缘应用方面取得进展。

哦,还有一件事。为了照顾 8 位机的普遍性,该开发板上的 LCD 接口 IC 和 CH552 USB 转 UART IC 都是预编程的 8 位微控制器。而 CH552 实际上就是一个古老的 8051。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum