利用 HyperBus 扩展微型物联网和可穿戴式设计中的存储器以节省空间和成本

投稿人:DigiKey 北美编辑

2018-08-01

随着物联网节点和可穿戴设备不断缩小,设计人员需要最大限度地利用微控制器的板载存储器来尽量节省电路板空间、功耗和成本。但是,存储器扩展有时是无法避免的。设计人员应考虑用 HyperBus 代替默认的 32 位控制器的总线结构;HyperBus 是一种高速、333 Mbps、8 位双倍数据速率 (DDR) 接口,可支持地址和数据处理。

尽管设计人员试图避免扩展,但在开发过程中由于存储器需求增加,常常有必要加以扩展。或者,为使设计在未来不会落伍,开发人员会预测未来的扩展需求。

借助 HyperBus,微控制器能够在同一总线上支持外部闪存和 RAM,而不像典型的 32 位接口那样使用 16 位数据总线和 16 位地址总线以及相关的控制引脚。它适用于任何具有 HyperBus 接口端口的存储器件,并且是一种高效易用的接口,支持空间受限的应用使用很少的引脚来扩展存储器。

虽然该总线的操作对固件是透明的,但新接触 HyperBus 的开发人员必须熟悉高速总线信号的操作以确保设计稳健。本文首先说明 HyperBus 的操作,然后介绍包含该接口的微控制器,并向用户展示如何有效地加以应用并测试其设计。

HyperBus 说明

如上所述,HyperBus 使用高速 8 位 DDR 接口来处理地址和数据。此外,每个存储器件都有相应的差分时钟、读/写锁存信号和片选。HyperBus 可在同一总线上支持外部闪存和 RAM,并且可配合任何具有 HyperBus 兼容外设接口的微控制器使用。

HyperBus 可设置成主/从接口,其中一个主机可以连接至总线上的一个或多个从存储器件。HyperBus 闪存器件称为 HyperFlash™,HyperBus DRAM 存储器件称为 HyperRAM™。

总线使用差分时钟,信号指定为 CK 和 CK#。由于 HyperBus 是 DDR 接口,数据在时钟的上升沿和下降沿都会传输。时钟仅由主器件驱动,其频率不得超过总线上最慢 HyperBus 存储器的额定时钟频率。

双向 8 位总线指定为 DQ[0-7],并在主从器件之间传输地址、数据和命令。双向读/写数据选通信号(指定为 RWDS)用于锁存数据。RWDS 由读取数据的器件控制,如果微控制器主机正在向 HyperRAM 写入数据,则 HyperRAM 控制 RWDS 信号。DQ[0-7] 上读取的数据与时钟的两个边沿对齐。

各从器件的选择是利用一个低电平有效片选信号(指定为 CS0#、CS1#、CS2# 等)。任何时候只有一个片选信号有效。所有总线事务都是由指定的片选信号从高电平变为低电平而启动。所有总线事务都是由指定的片选信号从低电平变为高电平而终止。开发人员必须确保任何时候只有一个片选信号处于有效状态。若非如此,可能会导致多个 HyperBus 从器件同时驱动 RWDS,这样会造成数据损坏。

低电平有效硬件复位信号(指定为 RESET#)由主器件驱动。拉低时,它会复位任何连接到该信号的外部 HyperBus 存储器件的状态,包括复位该存储器件的内部配置寄存器。但是,它不会影响 HyperBus 存储器件的内部存储器的状态。对于大多数 HyperBus 主微控制器接口,RESET# 不是 HyperBus 外设的一部分,而是一个通用 I/O 引脚。HyperBus 从器件的 RESET# 引脚上有一个弱上拉电阻,因此当浮空时,它会被拉至高电平状态。

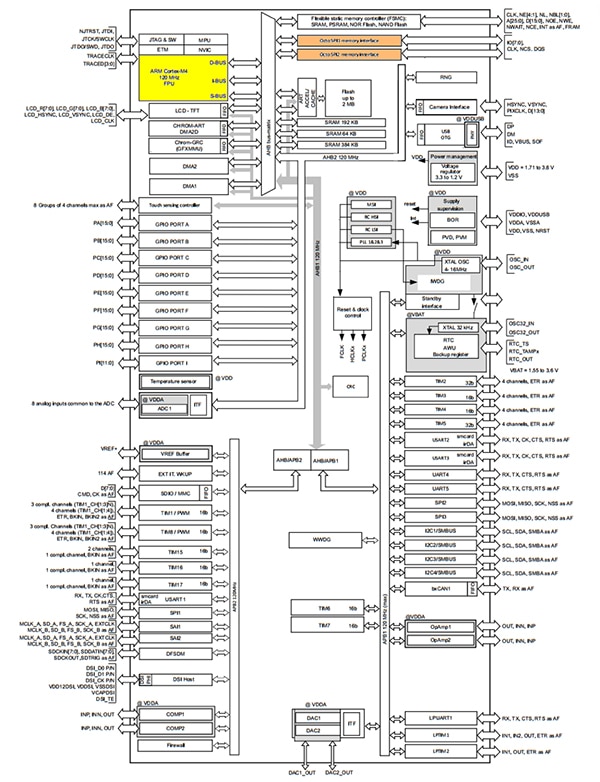

微控制器上任何与 HyperBus 兼容的外设都必须符合 HyperBus 规格。一个很好的兼容 HyperBus 的微控制器例子是 STMicroelectronics 的 STM32L4R9 Arm® Cortex®-M4F(图 1)。STM32L4R9 具有 2 MB 内部闪存和 640 KB SRAM。它有多种外设,包括两个可配置为 HyperBus 接口的 OctoSPI 接口。

图 1:STMicroelectronics STM32F4L9 微控制器基于带 FPU 的 Arm® Cortex®-M4 内核,具有两个兼容 HyperBus 的接口,此处以橙色突出显示。(图片来源:STMicroelectronics)

STM32L4R9 访问 HyperBus 外部存储器地址,将其作为映射到微控制器 AHB 总线地址空间的存储器,因此内核对外部存储器的读写操作与内部存储器相同。一旦配置好外部存储器件,HyperBus 的操作对内核便是透明的。

HyperBus 存储器全部是 16 位宽存储器,因此 STM32L4R9 的所有访问都必须在 16 位存储器边界上。STM32L4R9 主器件的数据访问可以是 16 位或 32 位,也必须在对齐的边界上。

HyperBus 上的典型读或写事务包括一系列连续的 16 位、一个时钟周期的数据传输,通过两个相应的 8 位宽、半时钟周期的数据传输实现,每个单端时钟沿或差分时钟交叉完成一个。读写事务总是传输完整的 16 位字数据。读数据字总是包含两个有效字节。写数据字的一个或两个字节可以屏蔽起来,以防止在写猝发期间写入个别字节。HyperBus 协议不支持字节传输,也不支持位分段等位操作。

STM32L4R9 上的每个 HyperBus 兼容端口都有一个专用 256 MB 存储器映射地址空间,映射如下:

HyperBus1 (OctoSPI1) 0x90000000 至 0x9FFFFFFF

HyperBus2 (OctoSPI2) 0x70000000 至 0x7FFFFFFF

对于要访问的 HyperFlash 或 HyperRAM 存储器件的内部地址,相对于上述位置的基本存储器地址发生偏移。例如,若 STM32F4L9 读取存储器位置 0x90000047,它将读回在 HyperBus1 上存储器位置 0x0047 访问的存储器件中存储的值。

Cypress Semiconductor 制定了 HyperBus 规格,而且还拥有 HyperBus 存储器产品线。Cypress S26KS512SDPBHI020 64 MB x 8 HyperFlash 存储器可以轻松连接到其中一个 OctoSPI 端口。它支持对最多 32 个 16 位字进行封装猝发访问。鉴于最大时钟速率为 166.6 MHz,S26KS512 HyperFlash 支持 333 MB/s 的最高持续读取速率。在 OctoSPI 的最大 60 MHz 时钟速率下,STM32L4R9 可以最高 120 MB/s 的速率读取任何外部 HyperBus 存储器。

如果通过 Cortex-M4 系统总线访问 HyperFlash,则 STM32L4R9 可以直接从该闪存执行代码。当用于代码存储器时,OctoSPI 支持集成预取缓冲器的 eXecute In Place (XIP),其从外部存储器加载下一存储器地址。

Cypress Semiconductor S27KS0641DPBHI020 8 MB x 8 HyperRAM 存储器是一款自刷新式 DRAM,可扩展 STM32L4R9 数据存储器。它支持对最多 64 个 16 位字进行封装猝发访问。S27KS0641 HyperRAM 还支持高达 333 MB/s 的持续读取速率,并且 STM32L4R9 可以最大 120 MB/s 的速率读取该存储器。

与 HyperBus 存储器接口

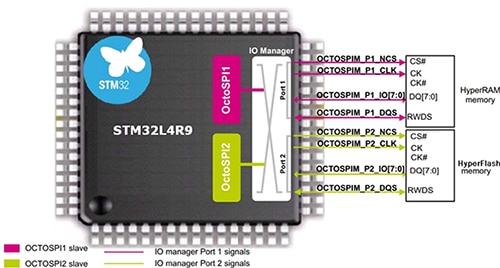

STM32L4R9 有两个 HyperBus 兼容端口,每个端口都可以单独连接到 HyperRAM 和 HyperFlash 外部存储器件(图 2)。RESET# 信号是可选的,因此图中没有显示。借助 Cypress HyperFlash 和 HyperRAM,STM32L4R9 可以轻松扩展内部存储器,同时对印刷电路板尺寸和设计复杂性的影响极小。

图 2:STM32L4R9 有两个 HyperBus 兼容端口,每个端口都可以单独连接到 HyperRAM 和 HyperFlash 外部存储器件。(图片来源:STMicroelectronics)

对布局布线来说,最重要的信号是 DQ[0-7] 和 RWDS。为获得最佳性能,这些信号在印刷电路板的微控制器和存储器之间的长度应尽可能短。

差分时钟信号 CK 和 CK# 应彼此相邻,并且对于信号全长,其间的间距应保持不变。如果可能,应使用 VSS 防护走线屏蔽 CK 和 CK#,以最大限度地降低 EMI。为了尽量减少阻抗不匹配,应使用下方的实心 VSS 层分接印刷电路板顶层上的所有信号。

HyperBus 开发新手最好添加探头测试点。对于 DQ[0-7] 和 RWDS,测试点应位于 STM32L4R9 微控制器和存储器件上。当 STM32L4R9 正在写入时,最好检查离存储器件最近的测试点。当 STM32L4R9 正在读取时,应检查离 STM32L4R9 最近的测试点。对于 CK、CK# 和 CS,应将测试点放在更靠近存储器件的位置。

由于 DDR 接口涉及高时钟频率,STM32L4R9 和存储器件的电压源必须尽可能无噪声。高噪声电源会影响信号时序并导致总线传输错误,因此建议使用去耦电容。HyperBus 存储器件为 I/O 引脚提供了单独的电源和接地,并且 I/O 电源 VCCQ 应增加 1 微法 (μF) 和 0.1 μF 电容(位于顶层或底层上)。

固件访问 HyperBus

HyperBus 存储器件具有片载寄存器,可用于设置器件的选项和时序。HyperBus 将这些寄存器称为配置寄存器 (CR)。所有 HyperRAM 器件都有内部 CR,允许设置某些操作特性。对于 HyperRAM S27KS0641,固件可以通过外部 8 位数据总线配置其低功耗模式、封装猝发长度、封装猝发类型、R/W 时序参数和输出驱动强度。

HyperFlash 虽然没有 CR,但有状态寄存器。S26KS512 HyperFlash 有三个状态寄存器。它支持使用内部纠错码 (ECC) 验证写操作,并具有 ECC 状态寄存器以指示写错误。另一个寄存器包含任何 ECC 错误的地址。第三个寄存器计数 ECC 纠错数和无法纠正的错误。所有这些寄存器都是只读寄存器。

HyperBus 事务支持两类存储器操作。第一类是读取或写入外部存储器。第二类是读取或写入 CR 或读取状态寄存器。

将 STM32L4L9 OctoSPI 配置为 HyperBus 端口后,内核便可访问存储器,像任何其他存储器映射位置一样。在存储器映射的 HyperBus 空间中,每次读或写操作都会启动微控制器和外部存储器之间的事务处理。每个 HyperBus 事务的开始都是微控制器通过命令/地址指令向外部存储器件发送三个 16 位字。命令/地址序列告诉外部存储器件操作是读还是写,是否正在寻址存储器空间或配置寄存器,事务是封装式还是线性猝发事务,并提供目标地址行和列。虽然这对带操作固件的微控制器都是透明的,但在调试期间,命令/地址序列很重要。

HyperBus 入门

开发人员了解 HyperBus 协议之后,建议利用评估板执行一些实验性编程,特别是新接触该接口的开发人员。适用于 STM32L4R9 微控制器的 STMicroelectronics STM32L4R9I-EVAL 评估板是一个很好的出发点(图 3)。HyperRAM 存储器件位于红圈中,器件的测试点位于右侧的针座连接器上。

图 3:STMicroelectronics STM32L4R9I-EVAL 可用于评估 STM32L4R9 微控制器。HyperRAM 存储器件位于红圈中,器件的测试点位于右侧的针座连接器上。(图片来源:STMicroelectronics)

STM32L4R9I-EVAL 具有丰富的特性,包括相机接口、两个 MEMS 麦克风、一个操纵杆和一个 4.3 英寸、480 x 272 像素彩色 TFT LCD 显示屏。该评估板支持 OctoSPI 接口,并有一个 ISSI 的 IS66WVH8M8BLL 64 Mb HyperRAM 器件焊接到印刷电路板。

总结

HyperBus 协议是一种合适且易用的接口,只需很少的引脚便可扩展空间受限应用的存储器。虽然该总线的操作对固件是透明的,但新接触 HyperBus 的开发人员必须熟悉高速总线信号的操作以确保设计稳健。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。