JK 触发器的工作原理

使用原始 Digi-Keyer 的实例

简介

触发器是以两个稳定状态存储单个二进制数据位的集成电路,广泛应用于计数器、寄存器、除法器以及顺序逻辑电路(又称为非稳态多谐振荡器),本文使用的实例就是这种电路。

触发器有多种类型可供选择,常见功能有设置和复位输入、清除、预设、时钟输入和互补逻辑输出。触发器由时钟输入的上升或下降沿跃迁触发。常见类型包括 SR 触发器、D 触发器或 T 触发器。JK 触发器有时被称为“通用”触发器,因为它们经过配置后可模拟多种其他类型的触发器。

JK 触发器功能

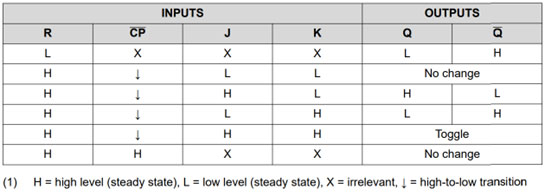

使用触发器时,须随时查阅器件规格书的真值表,以根据多个输入选项和时钟跃迁确定输出特征。例如,Texas Instrument 的 CD74HCT73E 是一款具有常见特征和易读取真值表的典型双 JK 触发器。

要记住两个基本事实:Q(带横线)或非 Q 输出始终是对 Q 输出的补充;只有 4 种 JK 输入配置能确定时钟输入从高电平到低电平跃迁时的输出。有关可能的 JK 配置,参见图 1。切换一词表示当 J 和 K 都为高电平且时钟从高电平到低电平跃迁时,Q 和非 Q 输出的当前状态翻转(真值表中条件 4)。

图 1.典型 JK 触发器规格书真值表。

图 1.典型 JK 触发器规格书真值表。

所述的基本真值未考虑复位 (R) 输入,此输入会在复位保持低电平时,为触发器提供初始状态。对于复位处于低电平时的时钟和 JK 输入,规格书中使用“无关”一词。这些输入的变化不会影响输出,直到复位保持高电平并接收到时钟跃迁。

思考重点:在触发器首次通电时,其输出不会自动设置为已知状态。由于无法预测会出现哪种输出状态,因此复位输入允许在通电后将输出初始化为已知状态。

顺序逻辑电路示例:摩斯字符生成器

三个 DIT 才能生成一个 DAH

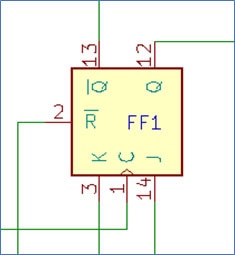

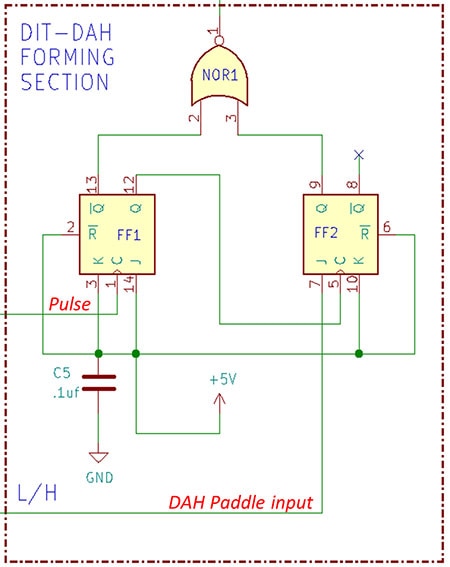

Digi-Keyer 摩斯字符生成器包含许多处理特定任务的元器件。为了演示触发器的作用,我们在称为 FF1 和 FF2 的触发器中加入了相关元件。关于 Digi-Keyer 的 DIT-DAH 字符形成部分的原理图,参见图 2。

图 2.Digi-Keyer 触发器字符形成电路

图 2.Digi-Keyer 触发器字符形成电路

在深入研究字符(DIT 和 DAH,又称为 DOT 和 DASH)的创建之前,必须先说明 NOR1 逻辑门的功能。NOR1 不仅是字符输出电路的第一级。当 NOR1 输出低电平时,它还能让定时电路向 FF1 发出规则脉冲。当 NOR1 输出高电平时,脉冲在电流计时周期末尾处停止。

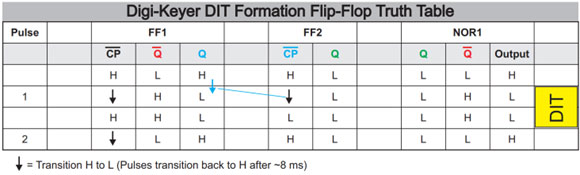

按下 DIT 翘板开关会触发从计时电路到 FF1 C 输入的初始高到低电平跃迁脉冲。因为两个 JK 输入都保持高电平,输出引脚 Q 和非 Q 发生切换。非 Q 触发 NOR1 输出低电平信号返回计时电路,表示 DIT 正在处理。计时功能完成时,另一个脉冲被发送到 FF1,将其切换回正常状态。DIT 形成期间,FF1 的 Q 输出触发 FF2 的 C 输入,但由于 DAH 翘板未按下(FF2 的 J 输入为低电平),FF2 的输出如图 1 真值表中的条件 3。图 3 罗列了生成单个 DIT 的结果顺序逻辑真值表。

图 3.顺序逻辑 DIT 形成真值表。

图 3.顺序逻辑 DIT 形成真值表。

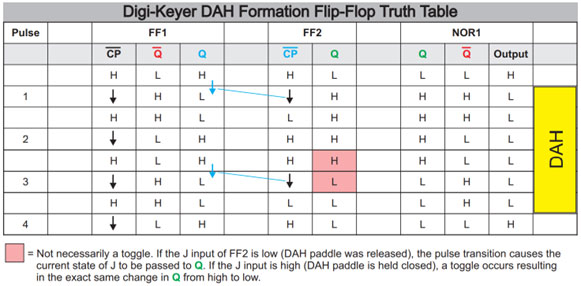

按下 DAH 翘板也会触发来自计时电路的初始脉冲,此脉冲会切换 FF1 并将 FF2 的 J 输入设置为高电平,从而导致 FF2 输出也会切换。由于 FF2 的 Q 输出还会触发 NOR1 输出低电平,因此会继续产生计时脉冲。FF1 和 FF2 都返回到正常状态需要三个 DIT 周期,在此之前,NOR1 的输出不会变回高电平。图 4 罗列了生成单个 DAH 的顺序逻辑真值表。

图 4.顺序逻辑 DAH 形成真值表。

图 4.顺序逻辑 DAH 形成真值表。

触发器返回正常状态的时长取决于高到低电平跃迁的时间。本例中,一个脉冲周期的低电平时间固定为 8 ms,但计时电路中的高电平时间可在 15 到 150 ms 之间调节。在最低设置时,DIT 字符约 158 ms 长,DAH 约为 474 ms。如果任意一个或两个翘板均保持闭合(高电平),让 FF1 和 FF2 回到正常状态的最后一次高到低电平跃迁会在 8 ms 内跃迁回高电平,这样两个字符之间就会有固定的间隙。

另一个思考重点:电路通电时,FF1 和 FF2 可能以随机的逻辑状态结束,如前所述。如果任何状态导致 NOR1 输出低电平,则计时电路将开始发送脉冲,直到 FF1 和 FF2 达到其正常状态。因此,触发器在通电后会自动初始化为正常状态,而无需使用复位输入。

总结

逐步跟踪触发器的逻辑可能比较困难,因此生成如图 3 和 4 的真值表有助于直观了解后台正在进行的操作。在本例中,执行了多步顺序逻辑,而未使用微控制器或固定、始终运行的时钟。触发器的输出就是存储的数据,需要刻意改变输入才能影响输出的变化。该数据也是易失性的。断电后数据丢失。摩斯字符生成器的目标并非生成数据。触发器用于记住上一个状态,以便在时钟脉冲从高到低跃迁期间确定下一个状态。

资源:

对构建 Digi-Keyer 和了解其工作原理感兴趣吗?DigiKey 在以下资源库中提供了全套计划、材料清单、编程代码、PCB 文件等:

https://media.digikey.com/pdf/Project%20Repository/Digikeyer.zip

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum