数据采集信号链仿真可简化元器件的选型和测试

投稿人:DigiKey 北美编辑

2025-11-24

过去,设计数据采集系统意味着从一摞数据表中寻找合适的元器件组合,并为拼凑的原型排除故障。现在,设计人员可以使用数字化设计工具,将传感器、模拟信号调节块、模数转换器 (ADC) 和数字滤波器等器件的型号拖放至虚拟信号链中,从而节省时间,减少弯路。该软件可仿真虚拟链输出,让设计人员了解所选组件如何影响结果,如信噪比 (SNR)、增益和失调误差以及功率等。

Analog Devices, Inc. (ADI) 的数字设计套件 Precision Studio(精密信号链设计套件)不译,包括 Signal Chain Designer( 信号链设计器)不译,该模块可帮助设计人员在创建数据采集系统之前进行仿真。在 Signal Chain Designer 中,用户可选择一个传感器,为模型设置参数,然后放入代表信号链组件的电路块中(图 1)。

图 1:使用 ADI Precision Studio 中的 Signal Chain Designer,设计人员可选择传感器,然后把相应电路块拖放到信号链中,进行数据采集组件仿真。(图片来源:Analog Devices, Inc.)

图 1:使用 ADI Precision Studio 中的 Signal Chain Designer,设计人员可选择传感器,然后把相应电路块拖放到信号链中,进行数据采集组件仿真。(图片来源:Analog Devices, Inc.)

传感器信号在转化为可靠数据前,需经过多级处理,每级由一个或多个电子元件或集成电路 IC 模块构成,为下一级预处理信号。最常见的处理级可放大模拟信号、过滤模拟信号、将模拟信号转换为数字信号以及过滤数字信号。

模拟信号放大级

由传感器产生的模拟信号往往与数据采集系统的最佳输入不匹配。模拟信号放大级使用运算放大器(运放)、全差分放大器、电压基准,以及电阻器、电容器和电感器等无源元件,将传感器信号转换成数据采集系统所需的有效形式。

在 Signal Chain Designer 中,用户可设定模拟放大级的输入和输出类型、所需增益以及实现正确电压输入所需的电平位移。然后,该软件使用 ADI 产品构建符合设定参数的电路,并输出原理图。

例如,对于图 1 中使用的 1 kΩ 阻抗、1 kHz 频率和 100 pF 电容的传感器,用户可设定增益为 2 V/V,电平偏移为 2.5 V(图 2)。

图 2:Signal Chain Designer 的用户设定模拟信号放大级的配置、增益、电平位移和其他参数。(图片来源:Analog Devices, Inc.)

图 2:Signal Chain Designer 的用户设定模拟信号放大级的配置、增益、电平位移和其他参数。(图片来源:Analog Devices, Inc.)

根据这些参数,该软件构建了模拟信号放大级的电路原理图(图 3,上),其中包含一个 ADA4097-2 运算放大器。ADA4097-2 系列运算放大器的每通道仅需 32.5 µA 电流,即可实现 130 kHz 的增益带宽积 (GBP),且 0.1 Hz 至 10 Hz 之间的峰峰值 (P-P) 噪声为 1,000 nV,典型的 1/f 噪声角频为 6 Hz。

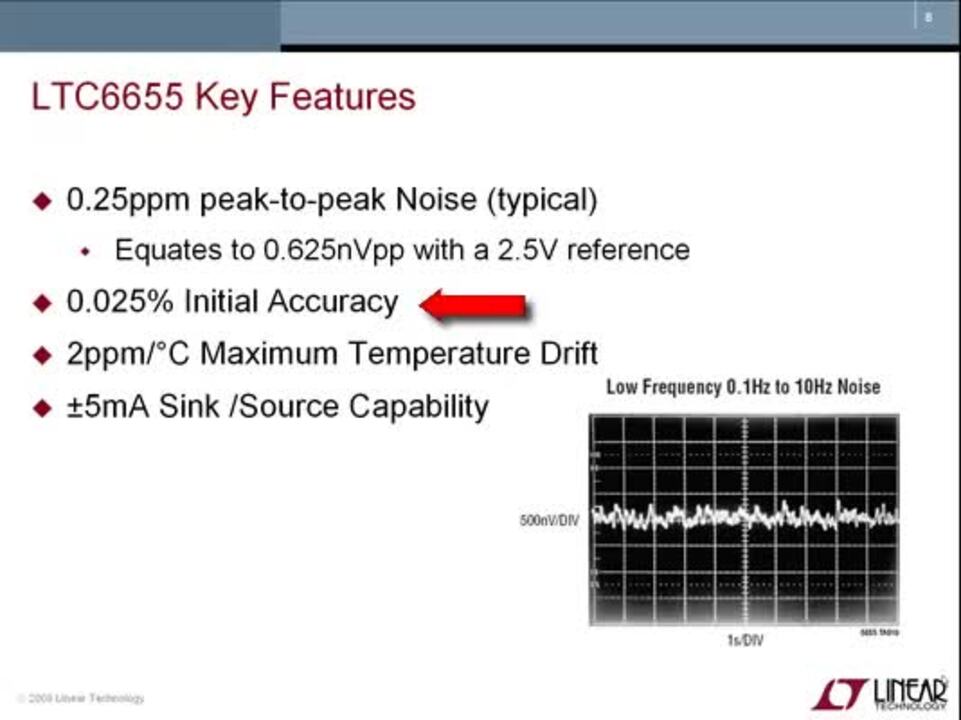

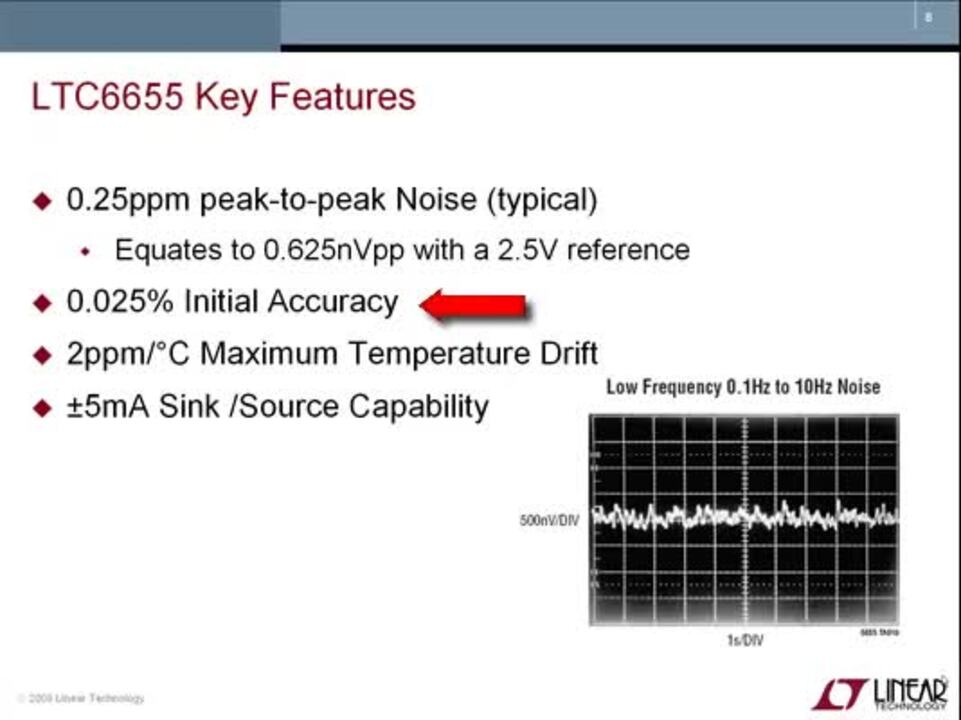

该软件还为放大器级开发了一个基准电路,其中包括一个 LTC6655B-2.5 精密带隙电压基准和一个 AD8510 运算放大器(图 3,下),这两个器件均来自 ADI。

图 3:Signal Chain Designer 的模拟信号放大级电路原理图,基于用户设定的规格,包括相应的 ADI 电子元件。(图片来源:Analog Devices, Inc.)

图 3:Signal Chain Designer 的模拟信号放大级电路原理图,基于用户设定的规格,包括相应的 ADI 电子元件。(图片来源:Analog Devices, Inc.)

LTC6655B-2.5 在 0.1 Hz 至 10 Hz 范围内的噪声为 625 nVP-P/0.25 ppmp-p,其最大精度为 ±0.025%、最大低压漂移为 2 ppm/°C,从而确保输出稳定的信号电压,而不受输入电压和负载变化的影响。AD8510 结场效应晶体管 (JFET) 运算放大器在 1 kHz 时的频谱噪声通常为 8 nV,只需 25 pA 的输入偏置电流,并能在 500 ns 内稳定在 0.1% 的误差带。

Signal Chain Designer 还允许用户设定信号在放大级的调节方式。用户可以配置全差分放大器、仪表放大器或电流检测放大器。

模拟信号滤波级

放大后的模拟信号必须经过滤波,以消除放大过程引起的噪音和失真。滤波器可以使用电阻器和电容器等无源元件来构建一阶滤波器,这种滤波器在截止频率后具有平缓的 -20 dB/decade 滚降。二阶和更高阶滤波器通常是有源滤波器,采用一个或多个运算放大器来实现更陡峭的滚降。

滤波器的配置将决定衰减高于中心频率 f0 的频率(低通)、低于 f0 的频率(高通)、两个截止频率之外的频率(带通),还是特定频带之外的频率(带阻或陷波)。如 Q 因子等其他滤波器参数,可进一步细化滤波器响应,确定滚降陡峭度、瞬态特性和通带形状。

在 Signal Chain Designer 中,用户可以通过选择滤波器类型和设定关键参数来配置简单滤波器的参数。Signal Chain Designer 的 Filter Wizard(滤波器向导)还可用来设计简单的三阶及以上滤波器,并将滤波器导入数字信号链设计中。在示例(图 4)中,用户选择了一个 f0 为 10 kHz、Q 系数为 0.707 的低通滤波器。所选的 Sallen-Key 型滤波器使用一个运算放大器连接高输入阻抗,并输出稳定性良好的低阻抗信号。

图 4:用户在 Signal Chain Designer 中定义模拟滤波级参数,包括滤波器类型、f0、Q 因子和增益。(图片来源:Analog Devices, Inc.)

图 4:用户在 Signal Chain Designer 中定义模拟滤波级参数,包括滤波器类型、f0、Q 因子和增益。(图片来源:Analog Devices, Inc.)

利用这些参数,Signal Chain Designer 输出一个包括 ADI LT6020 轨至轨运算放大器的电路(图 5)。LT6020 的电流消耗低于 100 µA,但仍能以 5V/µs 的压摆率快速响应输入信号的变化。在 -40°C 至 +125°C 的温度范围内,其 GBP 为 400 kHz。

图 5:Signal Chain Designer 输出的模拟信号滤波级电路,采用具有高压摆率和低功耗的 LT6020 运算放大器作为低通 Sallen-Key 二阶滤波器。(图片来源:Analog Devices, Inc.)

图 5:Signal Chain Designer 输出的模拟信号滤波级电路,采用具有高压摆率和低功耗的 LT6020 运算放大器作为低通 Sallen-Key 二阶滤波器。(图片来源:Analog Devices, Inc.)

模数转换级

在一个信号从传感器响应到生成数据的整个过程中,首先是将模拟信号转换成数字形式。常见 ADC 架构主要包括可在中等采样率下实现较高分辨率的逐次逼近寄存器 (SAR) 架构、可在较低采样速度下提供高分辨率的 Delta-Sigma (ΔΣ) 架构。要实现所需的数字输出,设计人员必须了解输入类型、系统分辨率和输出数据速率。

用户在 Signal Chain Designer 中设定好这些参数,该软件就会输出 ADC 电路,包括电压基准和输入端的无源电阻/电容 (RC) 滤波器。有些 ADC 还允许用户集成数字滤波功能,或将 ADC 设置为高阻抗 (Hi-Z) 模式,实现更简单、功耗更低的设计。

在示例(图 6)中, Signal Chain Designer 的输出确定了 ADI 的 ADR4525 电压基准和 AD7175-2 ΔΣ ADC。ADR4525 具有良好的温度稳定性,温度系数介于 0.8 ppm/°C 和 4.0 ppm/°C 之间,输出噪声在 2.048 VOUT 且 0.1 Hz 至 10 Hz 之间时为 1 µVp-p。AD7175-2 是一款 24 位 ADC,具有每秒 250,000 次采样 (250 kSPS) 的吞吐量和 20 µs 的建立时间。

图 6:在模数转换级, Signal Chain Designer 输出的电路中包括一个无源 RC 输入滤波器、一个电压基准和一个 ADC 模块。(图片来源:Analog Devices, Inc.)

图 6:在模数转换级, Signal Chain Designer 输出的电路中包括一个无源 RC 输入滤波器、一个电压基准和一个 ADC 模块。(图片来源:Analog Devices, Inc.)

在信号链的任何级中,用户都可以查看产品表,其中显示了相应的备用组件。例如,设计人员可以选用如 AD4008 等 SAR ADC 代替示例中的 ΔΣ ADC。AD4008 在 10 kSPS 时的功耗为 70 µW,在 2 MSPS 时为 14 mW(最大功耗)。在 Hi-Z 模式下,伪差分运行可实现 16 位精度,并简化了设计。

经过模数转换后,设计人员可在 Signal Chain Designer 的 ADC 下游设计中加入数字滤波块,从而优化输出。这些数字滤波块的选项包括均值滤波器、一阶和二阶滤波器以及简单的移动平均 CIC 滤波器。

使用 Signal Chain Designer 建立虚拟数据采集系统后,用户可在软件内针对频率响应、噪声、直流误差预算、功率和输入范围进行仿真。对于更多定制仿真,Signal Chain Designer 可以构建虚拟测试平台,并在 LTspice 中编辑和运行。

结语

象 ADI 的 Signal Chain Designer 这类数字工具,能极大减少构建精密数据采集系统时的反复试错与挫败感。借助软件内置的丰富、现成的运算放大器、电压基准源、ADC及其他元件模型,Signal Chain Designer 允许用户在虚拟环境中精细调整数据采集系统,确保向硬件选型与部署的平稳过渡。

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。