Challenges in Embedded System Design? A New Level of Integration in MCUs to Your Rescue!

2017-06-01

Embedded systems have become an indispensable part of life. Various innovations in embedded systems have opened up several new business opportunities, catching the attention of industry giants and startups. The growing business potential has motivated companies to invest in future product innovations. Embedded designers are under constant pressure to innovate in order to meet these market demands.

With the increased business potential, many companies have ventured into this space, creating intense competition. To differentiate, companies are focusing on enhanced product offerings and optimization for cost competitiveness.

Microcontrollers, the key component of an embedded system, must keep up with this challenge of evolving system needs. This has led to the introduction of PIC® microcontrollers with new levels of integration from Microchip Technology.

PIC Microcontrollers with Core Independent Peripherals

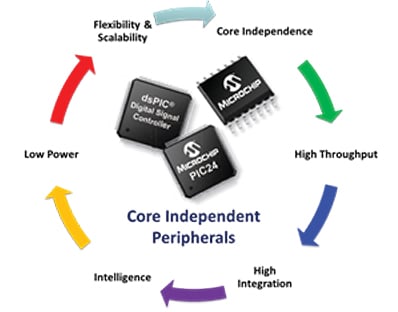

These new PIC microcontrollers, with the introduction of on-chip Core Independent Peripherals (CIPs), offer flexibility, scalability and enhanced performance to address the evolving needs to innovate, while still maintaining both low-power and cost competitiveness.

The CIPs offer enhanced performance, flexibility and scalability with the following features:

- Independent modules that function without the constant supervision of the central processing unit (CPU)

- Dedicated hardware for high throughput and near zero latency

- Direct interaction with other on-chip peripherals to implement self-sustaining closed-loop systems, offering higher integration

- Intelligent modules require almost no processor resources to function

- Low power consumption with the capability to operate in power saving modes, making them ideal for low-power design

Figure 1: Microchip’s PIC microcontrollers with CIPs offer several benefits

The CIPs are designed in hardware to implement the target functionality in a cost-effective manner. The incremental cost of designing a system function using the CIPs is much lower compared to similar implementation as user firmware requiring Flash, RAM, necessary processor bandwidth and external components. The CIPs allow PIC MCUs to perform extremely complex and dedicated tasks with little to no interaction with the CPU. This lowers overall power consumption while also freeing up the CPU to perform other tasks. In addition, CIPs facilitate significant BOM cost savings by replacing off-chip discrete components with the integrated peripherals. Also, the CIPs enable parallel processes to be implemented together with the CPU to accomplish complex functions, without the need for a costlier MCU with higher processing power.

Peripheral Integration in PIC Microcontrollers

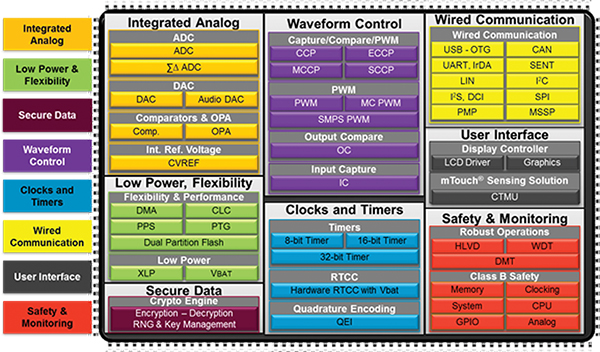

CIPs are found on many PIC MCUs including PIC16, PIC18, PIC24, dsPIC33 and PIC32MM families. Some of the CIPs included on 16-bit PIC24 and dsPIC33 devices include a Peripheral Trigger Generator (PTG), Configurable Logic Cells (CLC), crypto engine with Random Number Generator (RNG), high-speed comparators with blanking and digital filter functions, and Multiple Capture/Compare/PWM (MCCP).

Figure 2: Peripheral Integration in new PIC MCUs

Enhanced performance using the CIPs

Core Independent Peripherals reduce the processor resources requirement and allow for the implementation of parallel processes, leading to enhanced performance. For example, the crypto engine is capable of supporting AES, DES and 3DES symmetric encryption and decryption. In order to implement these routines in software, it requires about 1-6 KB of Flash and 100-400 Bytes of RAM. With the use of the crypto engine CIP, there is almost no Flash or RAM requirement and these resources are available to perform other functions of the end application.

Figure 3: Flash and RAM requirement for encryption/decryption

The crypto engine, being a hardware module, has a very high throughput compared to similar implementation in software. The crypto engine CIP carries out encryption and decryption approximately ten times faster than the software crypto implementation, while consuming almost the same amount of power. These are important factors for power-sensitive applications requiring highly secure data throughput. The high throughput at almost the same power consumption improves the overall energy efficiency of the application by approximately ten times. Since this CIP is also capable of operating in low-power modes when the CPU is in standby, it enables realization of overall lower system power in a battery-powered application requiring security, such as Internet of Things (IoT) applications.

CIPs for system capability extension and cost savings

The CIPs help in extending the system capabilities as the requirements evolve and facilitate innovations. The Peripheral Trigger Generator (PTG) is a user-programmable sequencer that generates triggers with complex inputs to coordinate the operation of other peripherals. Being “core independent”, the PTG addresses multiple system needs in one peripheral. The PTG reduces the need for CPU intervention and brings the flexibility and scalability to interface multiple peripherals into a closed-loop system, extending the capability of the overall system.

The PTG can be effectively used in implementing applications like integrated power factor correction in motor control. This application requires three PWM channels to control the motor functioning and an additional PWM to control the Power Factor Correction (PFC) operation. A simple Output Compare (OC) peripheral can be used to augment the number of PWM channels available on the device beyond the high-speed PWM channels. However, in an application such as PFC, optimal execution time is very important to complete the following tasks within a given window of time:

- Synchronizing motor control PWM and PFC PWM

- Triggering Analog-to-Digital Converter (ADC) actions and switching ADC channels used for motor control and PFC signals

Both of these requirements, synchronization as well as ADC trigger generation, are addressed effectively by a single PTG module. With PTG enabling integration of PFC with motor control, it also eliminates the need for a two-chip design, which significantly reduces the system level cost.

Energy efficiency

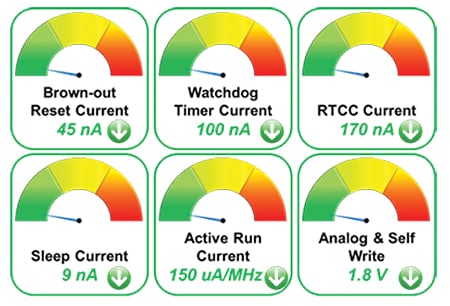

Portables, handheld devices, wearables and home security are some of the most popular IoT applications. These applications are battery-powered and must provide an extended life between recharging or replacement. Microcontrollers used in these applications must be power-optimized and flexible to implement energy efficient design. The new generation of eXtreme Low Power (XLP) PIC MCUs with CIPs offer the industry’s best low-power specifications to tackle low-power design requirements.

Figure 4: XLP PIC MCUs offer best-in-class power specifications

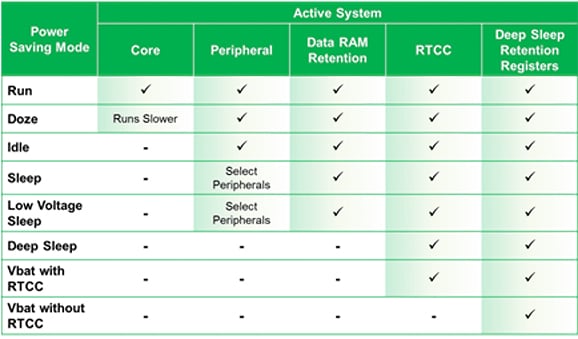

The XLP MCUs offer a range of low-power modes to address various design requirements. The XLP modes keep different resources of the MCU active as per the user configuration, while the remaining modules are powered down.

Figure 5: Power savings modes of XLP PIC MCUs

To augment the power conservation, CIPs in XLP PIC MCUs also consume minimal power to help in achieving low-power implementation.

Product offering enhancement using the CIPs

Due to intense competition, many embedded companies are on a quest to differentiate their products and enhance the product offerings, all while minimizing cost. The versatile CIPs enable product enhancements without additional overhead. For instance, in the case of improving the load bearing capability of drones, a higher rotation per minute (RPM) motor is needed. The higher RPM motor control typically demands an MCU with higher processing power and advanced analog features like high sampling rate and multi-channel ADC. However, the presence of CIP like High-Speed Comparators (HS Comparator) with blanking and digital filter functions together with precision voltage reference modules in an MCU eliminates the need to migrate to an advanced, costlier MCU. The peripheral combination acts as a threshold signal monitor and supervises the motor parameters efficiently. Since the HS Comparator has no lower sampling rate limitation of the normal ADC, it eliminates the need for the high-speed ADC in the MCU. As stated earlier, all of these advantages from CIP mitigate the need for additional processor resources and avoid the need to migrate to a costlier MCU.

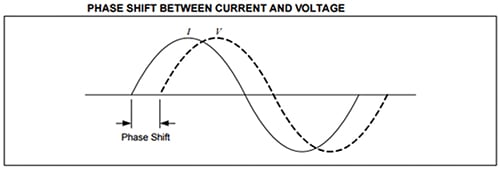

Another scenario of product enhancement is improving the accuracy of the utility energy meters. The accuracy of energy measurement in a utility meter depends on the accuracy of monitoring the phase difference between voltage and current signals to calculate the load power factor. The most common method to measure the phase difference between two signals is by comparing the time lapse between the two signals’ zero crossing and extrapolating the phase angles. For an accurate estimate of the phase difference, the sampling rate should be sufficiently high to minimize the extrapolation errors like in a high-speed ADC. The scenario gets even more complicated when a single ADC needs to sample all three signals – voltage, current and neutral – in a time division multiplexing method. In this case, the effective sampling rate requirement increases three-fold.

Figure 6: The phase shift is measured in a utility meter to determine power factor

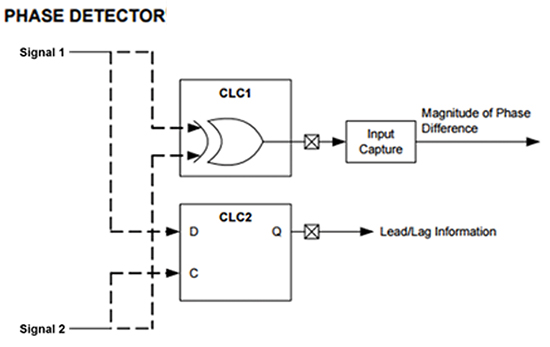

CIPs such as the Configurable Logic Cell (CLC) help in improving the accuracy of phase difference measurement by extending its capability to implement the hardware phase detector. The CLC with Input Capture (IC) peripheral can measure the phase difference between two signals of the same frequency. The combination of CIPs offers better resolution and gives lead/lag information as well. This extends the functionality of CLC-enable enhancements without the need to migrate to a more expensive, higher-performance MCU.

Figure 7: The phase detector CIP helps improve the accuracy of phase difference measurements

Design optimization

While the focus of embedded companies is on differentiation, the objective of system-level cost optimization cannot be compromised. PIC MCUs address this objective through various features.

Microchip’s PIC MCUs, with the CIPs, also include Integrated Analog Peripherals like on-chip sigma-delta ADC, high-speed SAR ADC and integrated operational amplifiers in a single chip with built-in control to make smart decisions without always requiring CPU-intervention. These integrated analog modules eliminate the need to create a multi-chip external components design. The integrated single-chip solution significantly reduces system level cost and saves PCB real estate offering better optimization. With a small PCB footprint, the solution can even address the requirements of space constrained applications such as wearables and sensor applications.

Further, the on-chip CIPs help in implementing several extended applications and off-load many of the deterministic routines from the CPU. Because of this, an application implementation using CIPs requires less processor resources like bandwidth, Flash and RAM. With the load removed from the CPU, the CIPs enable multiple parallel processes to be implemented without the expensive multi-core MCUs. The CIPs, being hardware modules, respond faster to stimuli and implement the target function with a higher throughput. All these attributes of CIPs mitigate the need to migrate to higher memory, higher processing capability MCUs and optimize the design cost.

Conclusion

With Microchip’s focus on innovation, PIC MCUs are constantly evolving to better fit the needs, both present and future, of our customers. The objective is not only to address future embedded systems’ technical requirements, but also to address the overall business challenges. The Core Independent Peripherals in PIC microcontrollers address the emerging needs and the challenges in the embedded systems and offer developers the flexibility to create groundbreaking applications.

免责声明:各个作者和/或论坛参与者在本网站发表的观点、看法和意见不代表 DigiKey 的观点、看法和意见,也不代表 DigiKey 官方政策。