代码下载

PS/2键盘接口逻辑: ps2_keyboard.vhd (5.1 KB)

消抖逻辑(必须包含在项目中):debounce.vhd (2.4 KB)

特性

- PS/2键盘接口的VHDL源代码

- 输出从键盘接收到的PS/2通码与断码

- 当新代码可用时设置标志输出

- 验证PS/2传输的奇偶校验位、起始位和停止位

- 可配置的系统时钟频率

- 同步PS/2时钟域与系统时钟域

- 对输入的PS/2信号进行消抖处理

引言

本文详述了用VHDL编写的、适用于CPLD和FPGA的PS/2键盘接口组件。该组件接收来自PS/2键盘的数据传输,并通过并行接口向用户逻辑提供键盘通码和断码。其设计采用Quartus II 12.1版本完成。图1展示了PS/2键盘接口集成到系统中的典型示例。此处提供了一个实现该PS/2键盘接口组件的示例设计,可将PS/2键盘转换为ASCII编码器。该PS/2键盘接口本身是此处提供的PS/2主机收发器的简化版本。

图 1. 示例实现

背景

PS/2(IBM个人系统/2)是一种通过6针Mini-DIN接口连接键盘和鼠标与PC兼容计算机系统的接口。计算机系统必须为键盘或鼠标提供5V电源和接地连接。通信通过2线串行接口进行,包括时钟线和数据线。两条线都需要上拉电阻(图1中显示为2kΩ)。图1中的120Ω串联电阻用于将3.3V FPGA I/O与5V信号进行接口。

键盘通电后,会执行自初始化序列。完成后即可通过PS/2接口传输键盘事件。

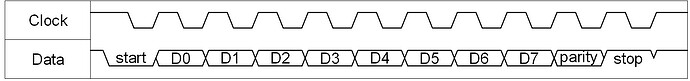

图2展示了事务格式。时钟信号和数据信号在非活动状态下均为逻辑高电平。键盘同时提供时钟信号和数据信号。时钟频率在10 kHz至16.7 kHz之间(即周期为60-100微秒)。数据以起始位(逻辑低电平)开始,后跟一个字节的数据、一个奇偶校验位,最后是停止位(逻辑高电平)。数据以最低有效位(LSB)优先发送。每个比特应在时钟信号的下降沿读取。完成后,时钟和数据信号均返回逻辑高电平。

图 2 。 PS/2键盘传输时序图

数据字节代表键盘扫描码的一部分:可能是通码(按键按下)或断码(按键释放)。存在三种不同的扫描码集,但绝大多数键盘使用附录中提供的扫描码集2。通码通常由一或两个字节组成。若通码使用两个字节,首字节为x"E0"。特定按键的断码通常与其通码相同,只是断码会在倒数第二字节处额外插入x"F0"字节。(PAUSE和PRNT SCRN键不遵循上述规则)

虽然可以向键盘发送数据(用于更改设置等),但通常无需此操作,本VHDL组件也未包含该功能。但此处提供的PS/2主机收发器组件可实现此功能。

操作原理

图3从概念上展示了PS/2键盘接口组件的架构。来自键盘的时钟信号和数据信号首先进行同步和消抖处理。(消抖组件的VHDL代码已在上文提供,文档可在此处查阅。)处理后的内部PS/2数据信号在PS/2时钟下降沿时被串行加载到移位寄存器中。空闲计数器用于判定传输何时结束,其定义为PS/2时钟信号保持高电平超过55微秒(即超过最坏情况下PS/2时钟周期的一半)。组合错误检查逻辑会验证起始位、停止位和奇偶校验位与数据的匹配性。当PS/2端口空闲且数据有效时,组件输出接收到的PS/2代码,并将ps2_code_new 信号置高以指示 ps2_code 总线上有新代码可用。该代码在总线上保持有效,直到接收到新代码。ps2_code_new 信号保持高电平,直到下一个PS/2事务开始(当PS/2时钟信号变低时会清零空闲计数器)。

图 3. PS/2键盘接口逻辑架构

端口描述

表1描述了PS/2键盘接口的端口定义。

表 1. 端口描述

设置时序参数

系统时钟频率会影响消抖时间和空闲计数器时序。ENTITY中声明的两个GENERIC参数clk_freq 和debounce_counter_size 必须正确设置,以确保组件正常运行。clk_freq 参数必须设置为系统时钟clk 的频率(以Hz为单位)。提供代码中的默认设置为50 MHz(该组件在此频率下进行了仿真和测试)。必须按照此处提供的消抖组件文档要求设置debounce_counter_size 参数,使2^debounce_counter_size/clk_freq=5微秒。对于50 MHz的系统时钟,debounce_counter_size = 8。

示例传输

图4展示了一个示例传输的时序图。当PS/2时钟信号变为低电平时,ps2_code_new 标志位会解除置位,表示新的PS/2键盘传输正在进行。事务完成后,ps2_code_new 标志断言,表示已接收到新的PS/2代码,并在ps2_code 总线上可用。本例中接收到的PS/2编码为x"1C",即"A"键的按下码。

图 4. PS/2通信示例

结论

该PS/2键盘接口是可编程逻辑元件,用于接收来自PS/2键盘的通信数据。它能同步时钟域、消除输入信号抖动、执行错误检查,并在键盘新编码通过并行输出总线就绪时通知用户逻辑。

附录:扫描码集 2

表 A1. 键盘扫描码集2

| 按键 | 按下码 | 释放码 |

|---|---|---|

| A | 1C | F0,1C |

| B | 32 | F0,32 |

| C | 21 | F0,21 |

| D | 23 | F0,23 |

| E | 24 | F0,24 |

| F | 2B | F0,2B |

| G | 34 | F0,34 |

| H | 33 | F0,33 |

| I | 43 | F0,43 |

| J | 3B | F0,3B |

| K | 42 | F0,42 |

| L | 4B | F0,4B |

| M | 3A | F0,3A |

| N | 31 | F0,31 |

| O | 44 | F0,44 |

| P | 4D | F0,4D |

| Q | 15 | F0,15 |

| R | 2D | F0,2D |

| S | 1B | F0,1B |

| T | 2C | F0,2C |

| U | 3C | F0,3C |

| V | 2A | F0,2A |

| W | 1D | F0,1D |

| X | 22 | F0,22 |

| Y | 35 | F0,35 |

| Z | 1A | F0,1A |

| 0 | 45 | F0,45 |

| 1 | 16 | F0,16 |

| 2 | 1E | F0,1E |

| 3 | 26 | F0,26 |

| 4 | 25 | F0,25 |

| 5 | 2E | F0,2E |

| 6 | 36 | F0,36 |

| 7 | 3D | F0,3D |

| 8 | 3E | F0,3E |

| 9 | 46 | F0,46 |

| ` | 0E | F0,0E |

| - | 4E | F0,4E |

| = | 55 | FO,55 |

| |5D | F0,5D | |

| BKSP | 66 | F0,66 |

| SPACE | 29 | F0,29 |

| TAB | 0D | F0,0D |

| CAPS | 58 | F0,58 |

| L SHFT | 12 | FO,12 |

| L CTRL | 14 | FO,14 |

| L GUI | E0,1F | E0,F0,1F |

| L ALT | 11 | F0,11 |

| R SHFT | 59 | F0,59 |

| R CTRL | E0,14 | E0,F0,14 |

| R GUI | E0,27 | E0,F0,27 |

| R ALT | E0,11 | E0,F0,11 |

| APPS | E0,2F | E0,F0,2F |

| ENTER | 5A | F0,5A |

| ESC | 76 | F0,76 |

| F1 | 5 | F0,05 |

| F2 | 6 | F0,06 |

| F3 | 4 | F0,04 |

| F4 | 0C | F0,0C |

| F5 | 3 | F0,03 |

| F6 | 0B | F0,0B |

| F7 | 83 | F0,83 |

| F8 | 0A | F0,0A |

| F9 | 1 | F0,01 |

| F10 | 9 | F0,09 |

| F11 | 78 | F0,78 |

| F12 | 7 | F0,07 |

| PRNT SCRN | E0,12,E0,7C | E0,F0,7C,E0,F0,12 |

| SCROLL | 7E | F0,7E |

| PAUSE | E1,14,77,E1,F0,14,F0,77 | -NONE- |

| [ | 54 | FO,54 |

| INSERT | E0,70 | E0,F0,70 |

| HOME | E0,6C | E0,F0,6C |

| PG UP | E0,7D | E0,F0,7D |

| DELETE | E0,71 | E0,F0,71 |

| END | E0,69 | E0,F0,69 |

| PG DN | E0,7A | E0,F0,7A |

| U ARROW | E0,75 | E0,F0,75 |

| L ARROW | E0,6B | E0,F0,6B |

| D ARROW | E0,72 | E0,F0,72 |

| R ARROW | E0,74 | E0,F0,74 |

| NUM | 77 | F0,77 |

| KP / | E0,4A | E0,F0,4A |

| KP * | 7C | F0,7C |

| KP - | 7B | F0,7B |

| KP + | 79 | F0,79 |

| KP EN | E0,5A | E0,F0,5A |

| KP . | 71 | F0,71 |

| KP 0 | 70 | F0,70 |

| KP 1 | 69 | F0,69 |

| KP 2 | 72 | F0,72 |

| KP 3 | 7A | F0,7A |

| KP 4 | 6B | F0,6B |

| KP 5 | 73 | F0,73 |

| KP 6 | 74 | F0,74 |

| KP 7 | 6C | F0,6C |

| KP 8 | 75 | F0,75 |

| KP 9 | 7D | F0,7D |

| ] | 5B | F0,5B |

| ; | 4C | F0,4C |

| ’ | 52 | F0,52 |

| , | 41 | F0,41 |

| . | 49 | F0,49 |

| / | 4A | F0,4A |

相关主题

PS/2主机收发器(VHDL)

PS/2键盘转ASCII转换器(VHDL)

PS/2鼠标接口(VHDL)

消抖逻辑电路(VHDL)