代码下载

PS/2主机收发器(顶层文件):ps2_transceiver.vhd (11.2 KB)

消抖逻辑(必须同时包含在项目中):debounce.vhd (2.4 KB)

特性

- PS/2主机收发器的VHDL源代码

- 输出从PS/2设备接收到的PS/2编码

- 当有新接收到的编码可用时设置标志输出

- 验证接收数据的奇偶校验位、起始位和停止位

- 接收并向PS/2设备发送命令

- 在传输操作进行中/完成时通知用户

- 可配置的系统时钟频率

- 同步PS/2时钟域与系统时钟域

- 对输入的PS/2信号进行消抖处理

引言

本文详述了用于CPLD和FPGA的PS/2主机收发器组件,采用VHDL编写。该组件接收来自PS/2设备的数据事务,并通过并行接口将PS/2数据提供给用户逻辑。同时通过并行接口接收用户逻辑的命令,并按照PS/2协议将其传输至PS/2设备。设计使用Quartus II 13.1版本完成。图1展示了PS/2主机收发器集成至系统的典型实例。此处提供的PS/2鼠标接口采用本PS/2主机收发器,用于从标准PS/2鼠标获取数据流。此处提供的PS/2键盘接口实现了简化版PS/2主机收发器设计(仅使用接收逻辑,无发送功能)。

图 1. 示例实现

背景

PS/2(IBM个人系统/2)是一种通过6针Mini-DIN接口连接键盘和鼠标与PC兼容计算机系统的接口。计算机系统必须为键盘或鼠标提供5V电源和接地连接。通信通过2线串行接口进行,包括时钟线和数据线。两条线都需要上拉电阻(图1中显示为2kΩ)。图1中的120Ω串联电阻用于将3.3V FPGA I/O与5V信号进行接口。

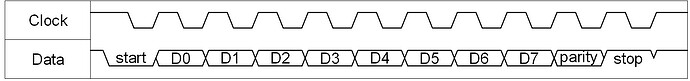

图2展示了接收事务的格式。在非活动状态下,时钟和数据信号均为逻辑高电平(注意上拉电阻)。设备同时提供时钟和数据信号。时钟频率在10 kHz至16.7 kHz之间(即周期为60-100微秒)。数据以起始位(逻辑低电平)开始,后跟一个字节的数据、一个奇偶校验位,最后是停止位(逻辑高电平)。数据以最低有效位(LSB)优先发送。每个比特应在时钟信号的下降沿读取。完成后,时钟和数据信号均返回逻辑高电平。

图 2 。 PS/2接收时序图

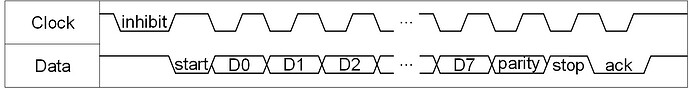

图3展示了发送事务的格式。主机首先通过将时钟线拉低100微秒来请求发送数据。这会抑制PS/2总线。在100微秒的抑制后,主机释放时钟并在数据线上输出一个低电平起始位。然后设备开始生成时钟脉冲。在每个下降沿,主机依次移出数据位(LSB优先),后跟奇偶校验位。在下一个时钟周期,主机释放数据线,数据线被上拉电阻拉高以表示停止位。设备在时钟上升沿读取这些信号后,发出一个逻辑低电平确认位,向主机反馈已接收数据。主机在最后一个下降沿读取该确认位,随后设备释放时钟和数据线,使其返回逻辑高电平。

图 3. PS/2发送时序图

操作原理

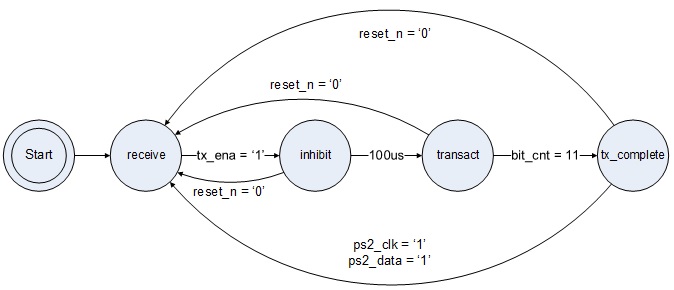

图4展示了PS/2主机收发器的状态图。该组件在不执行发送事务时始终处于接收状态。在此状态下,它可以检测设备发起的事务,接收数据,并将其输出到用户逻辑。如果用户逻辑通过置位tx_ena 信号请求发送事务,主机将锁存数据并进入一系列执行发送事务的状态。首先进入抑制状态,在此状态下将PS/2时钟线抑制100微秒。此后进入事务状态,发送数据和奇偶校验位,并评估设备的确认位。最后进入tx_complete 状态,等待设备释放PS/2总线后返回接收状态。

图 4. 状态图

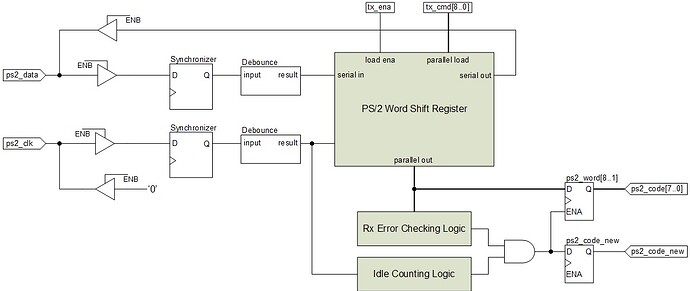

图5概念性地展示了PS/2主机收发器的操作。来自PS/2时钟和数据端口的输入信号经过同步和消抖处理。(消抖组件的VHDL代码已在上文提供,文档可在此处查阅。)处理后的内部PS/2数据信号在PS/2时钟下降沿时被串行加载到移位寄存器中。在接收状态下,空闲计数器通过检测PS/2时钟保持高电平超过55微秒(即超过最坏情况下PS/2时钟周期的一半)来判断事务结束。组合错误检查逻辑会验证起始位、停止位和奇偶校验位是否与对应数据匹配。当PS/2端口空闲且数据有效时,组件输出接收到的PS/2代码,并将ps2_code_new 信号置高以指示 ps2_code 总线上有新代码可用。该代码在总线上保持有效,直到接收到新代码。ps2_code_new 信号保持高电平,直到下一个PS/2事务开始(当PS/2时钟信号变低时会清零空闲计数器)。

图 5. 概念架构

当请求发送事务时,tx_cmd 总线上提供的发送数据和奇偶校验位会被加载到移位寄存器中。抑制状态会在PS/2时钟线上输出低电平以抑制总线。在传输状态下,PS/2时钟被释放,移位寄存器中的命令在PS/2时钟下降沿时被串行移出至PS/2数据线。对位进行计数,并在适当时刻释放数据线以接收设备的确认位。

端口描述

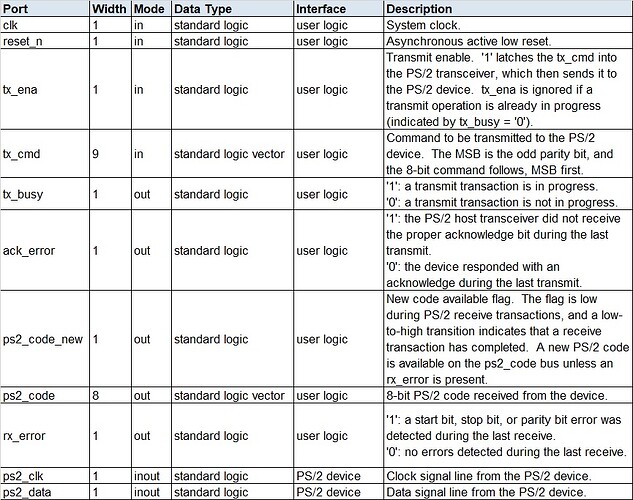

表1描述了PS/2主机收发器的端口。

表 1. 端口描述

设置时序参数

系统时钟速度影响主机收发器的时序操作。ENTITY中声明的两个GENERIC参数clk_freq 和debounce_counter_size 必须正确设置,以确保组件正常运行。clk_freq参数必须设置为系统时钟clk 的频率(以Hz为单位)。提供代码中的默认设置为50 MHz(该组件在此频率下进行了仿真和测试)。debounce_counter_size 参数必须满足2^debounce_counter_size / clk_freq = 5us。对于50 MHz的系统时钟,debounce_counter_size = 8。

示例事务

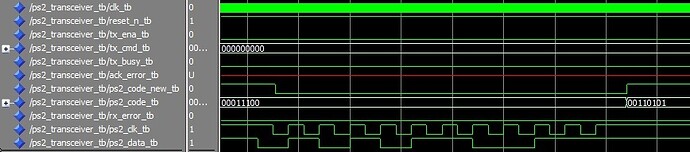

图6显示了一个示例接收事务的时序图。一旦PS/2时钟信号变低,ps2_code_new 标志取消断言,表示新的PS/2接收事务正在进行。事务完成后,ps2_code_new 标志断言,表示已接收到新的PS/2代码,并在ps2_code 总线上可用。在此情况下,接收到的PS/2代码为x“35”。rx_error 信号保持低电平,表示事务期间未检测到错误。

图 6. 示例PS/2接收事务

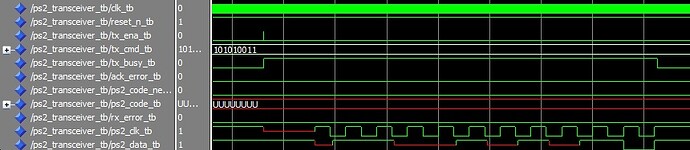

图7显示了一个示例发送事务的时序图。一旦用户逻辑断言tx_ena 输入,PS/2主机收发器就会锁存tx_cmd 端口上的命令。tx_busy 信号变高,表示发送事务正在进行,用户逻辑可以取消断言tx_ena 信号。收发器执行该事务。完成后,它将撤销tx_busy 输出信号,表明事务已完成且收发器再次可用。ack_error 信号保持低电平,表明PS/2设备在事务结束时发出了预期的确认位。

图 7. PS/2发送事务示例

结论

该PS/2主机收发器接口是可编程逻辑组件,用于处理与PS/2设备的事务。它同步时钟域、消除输入信号抖动、执行错误检查、发送命令、接收数据,并在设备的新数据通过并行输出总线可用时通知用户逻辑。

相关主题

PS/2键盘接口(VHDL)

PS/2键盘转ASCII转换器(VHDL)

PS/2鼠标接口(VHDL)

消抖逻辑电路(VHDL示例)