代码下载

DAC DAC121S101 Pmod控制器(顶层文件): pmod_dac121S101.vhd (8.3 KB)

双MOSI接口的SPI主控制器(必须包含在项目中): spi_master_dual_mosi.vhd (9.7 KB)

特性

- 用于Digilent Pmod DA2(德州仪器DAC121S101数模转换器的Pmod模块)的简化接口VHDL源代码

- 通过简单并行接口同时控制Pmod模块的两个12位DAC

- 处理与DAC Pmod的所有串行通信

- 可配置系统时钟频率

简介

详述了用于连接Digilent Pmod DA2与DAC121S101的VHDL组件,如图1所示。图2展示了该DAC Pmod控制器集成到系统中的典型示例。如图所示,DAC Pmod控制器连接Pmod端口并执行指令来设置DAC输出。数据通过简单并行接口锁存,可连接至用户逻辑或FPGA的输入端口。

图 1. Digilent Pmod DA2适配DAC121S101

图 2. 示例实现

背景

Pmod DA2模块配备了两个德州仪器12位DAC121S101数模转换器。转换器采用供电电压作为基准电压,并内置轨到轨输出摆幅的片上放大器。通过最高30MHz的串行接口进行控制。

操作原理

DAC Pmod控制器采用简易状态机,并基于技术论坛提供的SPI主控组件修改版本来控制DAC Pmod。

状态机

该设计采用图3所示的状态机实现其操作。组件启动后立即进入开始( start ) 状态。在此状态保持100微秒,确保Pmod有充足的上电时间。随后进入暂停( pause ) 状态。此处确保DAC之间的两次事务处理至少有20纳秒间隔。此时,控制器会取消忙碌( busy ) 信号的置位,表明DAC Pmod控制器已准备好与DAC Pmod进行新的事务处理,并进入就绪( ready ) 状态。在就绪( ready ) 状态等待,直到dac_tx_ena 使能信号激活时,锁存新事务数据并进入发送数据( send_data ) 状态。在此状态下执行与Pmod的事务后,返回暂停( pause ) 状态。虽未图示,但任何时候重置组件都会使其返回开始( start ) 状态。

图 3. 状态图

SPI 主控

在send_data 状态期间,状态机控制一个SPI主设备组件与Pmod上的DAC进行通信。本设计中使用的SPI主设备是经过修改的流行SPI主设备版本,其文档和资源可在此处获取。此修改版本复制了原始版本中的MOSI逻辑,以提供两个独立的MOSI输出(mosi_0 和mosi_1 )。输出的MOSI数据分别取自两个并行输入tx_data_0 和tx_data_1 。通过这种方式,SPI主设备可以使用单个SPI总线同时与两个独立的从设备进行独立数据通信。

SPI主控器配置为CPOL=0且CPHA=1,以满足DAC121S101转换器的要求。

时钟配置

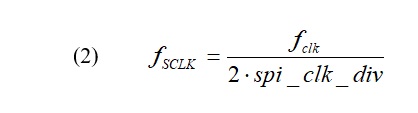

通过为ENTITY中定义的GENERIC参数clk_freq 和spi_clk_div 赋值,配置该DAC Pmod控制器的时钟。clk_freq 参数必须设置为clk 输入端口提供的系统时钟频率(单位MHz)。公式1定义了spi_clk_div 值的计算方法。

其中fclk 表示所提供系统时钟的频率,单位为MHz。

例如,代码中指定的默认值为spi_clk_div = 1。这是因为该组件是在使用50 MHz系统时钟的情况下开发和测试的。50/60 = 0.83,向上取整为1。任何clk_freq ≤ 60 MHz都会导致默认的spi_clk_div = 1。

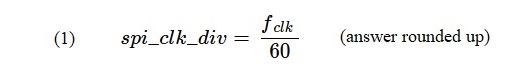

公式2定义了由此产生的串行时钟频率fsclk 。

此计算确保串行时钟低于DAC规定的最大通信频率30 MHz。当输入时钟频率(以MHz为单位)为60的整数倍时,通信速度最快。

事务

DAC Pmod控制器通过其busy 口输出指示其可用性。当busy 信号为’0’时,控制器准备接受发送到DAC Pmod的事务。置位dac_tx_ena 输入信号将锁定dac_data_a 和dac_data_b 上的当前值。一旦锁存,控制器会置位busy信号,表示正在进行事务,当前不可用。当事务完成时,控制器再次取消busy 信号的置位,表示已准备好接受下一个请求。

事务示例

图4展示了一个事务示例。busy 信号为’0’。用户逻辑随后提供数据"100110011001"写入DAC A,以及"010110110011"写入DAC B。控制器置位busy 信号表示请求已锁存,此时用户逻辑可撤销dac_tx_ena 信号。控制器向DAC Pmod发送串行通信,完成后取消busy 信号的置位。之后,用户逻辑发起新事务,将"010110010001"写入DAC A,并将"101100111110"写入DAC B。

若dac_tx_ena 信号未撤销,新的事务请求将在控制器就绪20纳秒后被锁存并开始执行。

图 4. 事务处理示例

端口描述

表1描述了DAC Pmod控制器的端口。

表 1. 端口描述

连接方式

该Pmod配备一个6针连接器J1。表2提供了该连接器的引脚定义。需将DAC Pmod控制器的端口分配至FPGA引脚,这些引脚已按所列方式路由至连接器。

表 2. DAC Pmod引脚定义及与DAC Pmod控制器的连接

复位

reset_n 输入端口必须保持逻辑高电平,DAC Pmod控制器组件才能运行。该端口低电平时将异步复位组件。复位期间,组件会中止与DAC Pmod的当前事务,并将busy 输出置高表示不可用。复位释放后,DAC Pmod控制器将重新开始运行。

结论

该DAC Pmod控制器是一个可编程逻辑组件,用于连接Digilent的Pmod DA2与DAC121S101转换器。它通过简单的并行接口接收用户输入,同步控制Pmod上的两个转换器。