代码下载

版本1.2: spi_master.vhd (8.9 KB)

当总线空闲时,SCLK立即采用CPOL输入的值

版本1.1: spi_master_v1_1.vhd (8.8 KB)

修正了ModelSim仿真错误(显式重置clk_toggles信号)

版本1.0: spi_master_v1_0.vhd (17.0 KB)

首次公开发布

特性

- 串行外设接口(SPI)主控组件的VHDL源代码

- 可配置从机数量

- 可配置数据宽度

- 可选极性和相位

- 可选速率

- 适用于长数据流的连续模式

简介

本文详述了用于CPLD和FPGA的SPI主控组件,采用VHDL编写。该组件使用Quartus II 9.0版本设计。资源需求取决于具体实现(即所需的从机数量和数据宽度)。图1展示了SPI主控集成到系统中的典型示例。

图 1. 应用示例

背景

SPI通信方案采用四线制全双工数据链路。主机通过拉低从机选择(SS)线来启动传输。由主机驱动的串行时钟(SCLK)线提供同步时钟源。主机通过主出从入(MOSI)线发送数据,通过主入从出(MISO)线接收数据。

主机可通过多种技术与多个从机通信。最常见配置中,每个从机有独立的SS线,但与其他从机共享SCLK、MISO和MOSI线。当从机的SS线未被拉低时,该从机会忽略共享线路。该拓扑结构如上图1所示。

SPI有四种工作模式,基于两个参数:时钟极性(CPOL)和时钟相位(CPHA)。主从设备必须使用相同模式才能清晰通信。若CPOL为0,则SCLK通常为低电平,首个时钟边沿为上升沿。若CPOL为1,则SCLK通常为高电平,首个时钟边沿为下降沿。CPHA定义数据对齐方式。若CPHA为0,则首个数据位在SS下降沿写入,在首个SCLK边沿读取。若CPHA为1,数据在首个SCLK边沿写入,在第二个SCLK边沿读取。图2的时序图展示了四种SPI模式。

图 2. SPI时序图

端口描述

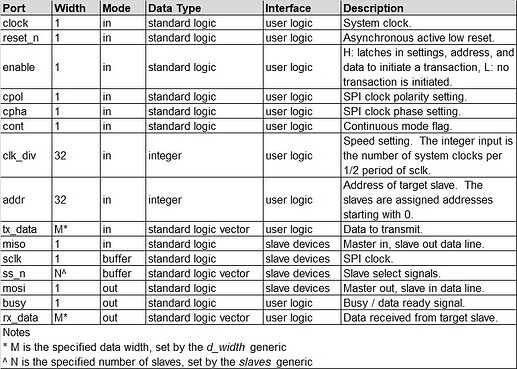

表1描述了SPI主设备的端口。从设备数量通过GENERIC参数slaves 在ENTITY中声明,发送和接收数据总线宽度则由GENERIC参数d_width 声明。

表 1. 端口描述

时钟控制

clock 与clk_div 输入共同定义SCLK频率(即SPI数据速率)。clock 是用于驱动组件内部同步逻辑的系统时钟。clk_div 整数输入允许用户设置当前事务的相对速度。如公式1所述,clk_div 表示SCLK跳变之间的时钟周期数。

当clk_div 端口设为1时,SCLK频率为时钟频率的一半,此时数据速率达到最大值。enable 引脚将clk_div 值锁存至组件以启动每个事务,因此可为不同从设备单独调整数据速率。

将clk_div 端口设为常量值可永久固定数据速率。若clk_div 设为0,组件将默认采用1作为参数值。因此,将clk_div 端口拉低可配置该组件始终以最高速度运行。

极性与相位

使能 引脚在每个事务开始时锁存cpol 和cpha 的标准逻辑值。这使得能够使用独立的SPI模式与各个从设备通信。若所有从设备需要相同模式,只需将cpol 和cpha 连接到相应逻辑电平。

事务处理

busy 输出端口的低电平表示组件已准备好接收命令。该组件在使能输入信号有效的第一个时钟上升沿锁存事务的配置、地址和数据。随后的时钟周期中,组件将置位busy 信号并开始执行事务。完成后,组件会在rx_data 端口输出接收到的数据。这些数据将保持在端口上,直到组件从后续事务中接收到新数据。当数据可用时,组件将busy 信号置低以通知用户,并立即准备好接收下一条指令。

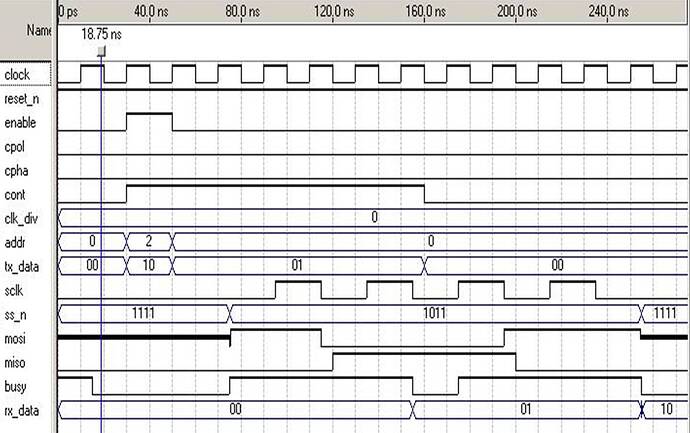

图3展示了一个典型事务的时序图。此SPI主设备实例化时配置了四个从设备,数据宽度为四位。它向工作在SPI模式3(CPOL=1,CPHA=1)的从设备2发送数据"1001"。主设备接收到"1010"数据。

图 3. 典型事务时序图

连续模式

在最后一位接收位期间,SPI主设备读取cont 标志 。若为低电平,组件按上述方式完成通信。若为高电平,组件会锁存tx_data 端口的新数据,并在当前数据传输完毕后无缝衔接新数据的传输。当当前数据的最后一位传输完成时(即新数据的第一位出现在mosi端口),组件会在rx_data 端口输出第一块接收数据,并将busy 信号置为无效一个时钟周期以指示该接收数据可用。接收数据将保持在rx_data 端口,直到新数据通信完成且组件呈现下一块接收数据。

图4展示了使用连续模式的事务时序图。此SPI主设备实例化时配置了四个从设备,数据宽度为两位。当组件锁存初始数据"10"后,cont 端口保持高电平,tx_data 端口呈现新数据"01"。当组件锁存新数据后,会将busy 端口置为低电平,这表明cont 和tx_data 端口可以清空,同时第一个接收数据"01"已出现在rx_data 端口上。事务处理完成后,busy 信号再次解除,新的rx_data 数据"10"准备就绪。

图 4. 连续模式下的时序图

连续模式通过持续运行可实现超长数据流的传输。将cont 端口置为低电平可禁用连续模式。

复位

SPI主控组件工作时,reset_n 输入端口必须保持逻辑高电平。该端口的低电平信号会异步复位组件。复位期间,组件将busy 端口和所有ss_n 输出保持高电平。此时mosi 输出呈现高阻态,rx_data 输出端口数据清空。复位释放后,busy 端口在下一个时钟周期解除断言,表示SPI主控已准备好通信。

结论

该SPI主控器是可编程逻辑组件,通过单一并行接口适配多种从设备通信。支持与用户指定数量的从机通信,各从机可配置独立SPI模式、数据位宽及串行时钟速率。

相关主题

加速度计ADXL345 Pmod控制器(VHDL) - 该设计使用本页描述的SPI主控组件与ADI公司ADXL345加速度计通信。同时展示了该SPI主控器的连续模式功能。

加速度计ADXL362 Pmod控制器(VHDL) - 该设计使用本页描述的SPI主控组件与ADI公司ADXL362加速度计通信。同时展示了该SPI主控器的连续模式功能。

环境光传感器Pmod控制器(VHDL) - 该设计通过SPI主控组件连接TI公司ADC081S021模数转换器,采集Vishay半导体TEMT6000X01环境光传感器数据。

ADC AD7476A Pmod控制器(VHDL) - 该设计采用改进版SPI主控组件,额外增加第二条MISO数据线。双数据输入线设计可同时与两个ADI公司AD7476A 12位ADC进行通信(接收数据)。

DAC AD5541A Pmod控制器(VHDL)- 该设计使用上述SPI主控与模拟器件公司AD5541A单通道16位数模转换器通信。

DAC AD5628 Pmod控制器(VHDL)- 该设计使用上述SPI主控与模拟器件公司AD5628 12位数模转换器通信。它配置转换器并发送命令、地址和数据以控制转换器的8个通道。

DAC AD7303 Pmod控制器(VHDL)- 该设计使用经过修改包含第二条MOSI数据线的SPI主控组件版本。该设计可同时控制2个独立的模拟器件公司AD7303双通道8位DAC。

DAC DAC121S101 Pmod控制器(VHDL)- 该设计使用经过修改包含第二条MOSI数据线的SPI主控组件版本。通过两条数据输出线,该设计可同时向2个独立的德州仪器DAC121S101 12位数模转换器发送数据。

数字电位器AD5160 Pmod控制器(VHDL)- 该设计使用上述SPI主控调节模拟器件公司AD5160数字电位器的阻值。

陀螺仪L3G4200D Pmod控制器(VHDL)- 该设计使用上述SPI主控配置并读取ST微电子L3G4200D陀螺仪的数据。同时展示了该SPI主控器的连续模式功能。

摇杆JSTK2 Pmod控制器(VHDL)- 该设计使用上述SPI主控向摇杆模块内嵌的PIC16F1618微控制器发送命令并获取数据。

导航Pmod控制器(VHDL)- 该导航设计使用上述SPI主控从ST微电子LPS25HB压力传感器和LSM9DS1 iNEMO惯性模块(3轴加速度计、陀螺仪和磁力计)获取数据,提供总计10个自由度。

热电偶Pmod控制器(VHDL)- 该设计使用上述SPI主控读取美信MAX31855热电偶数字转换器的数据。