特性

以下主题通过Lattice Diamond ver.2.0.1设计软件进行讲解。

• Booth Radix-4时序乘法器概述

• 状态机结构与Booth算法应用

• Booth Radix-4字宽可扩展性

• 使用测试平台验证乘法器

简介

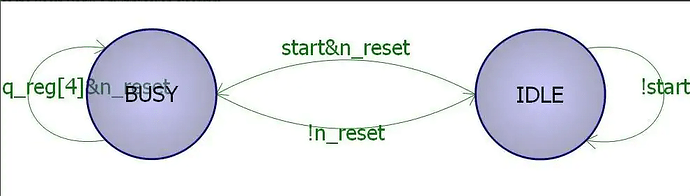

该Verilog模块采用简单的2状态有限状态机(FSM),通过评估乘积寄存器中的3位分组来选择五种可能的运算之一。图1展示了这个2状态FSM的状态图。这种3位重编码的移位相加过程被称为Booth算法。本模块采用的版本称为Booth Radix-4乘法算法。

图 1 – Booth Radix-4 FSM 状态图

背景

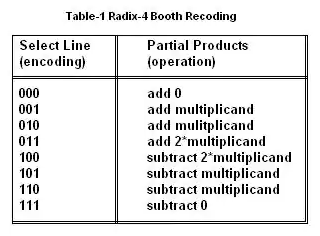

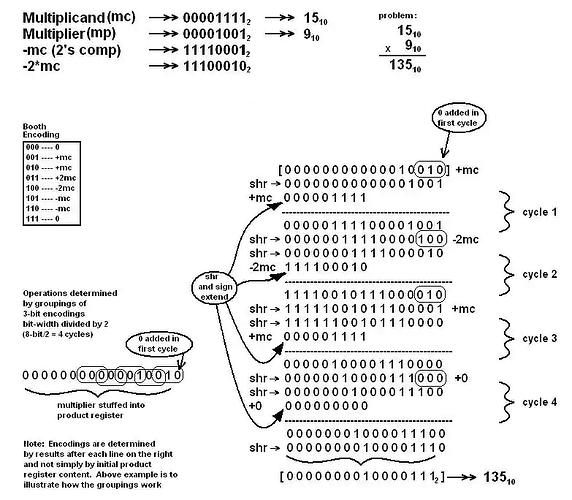

Booth Radix-4算法在保持电路复杂度最低的同时,将部分积数量减少了一半。这使得FPGA或CPLD能以更低功耗运行,并在没有硬件乘法器(如本例使用的Lattice MachXO2 PLD)时实现乘法运算。Booth重编码通过跳过不产生新乘积项的时钟周期来实现这些优势。Radix-4 Booth重编码本质上是一个多路复用器,根据乘积寄存器中的位分组选择正确的移位相加操作。乘积寄存器存储的是乘数。基于重编码值,将被乘数及其二进制补码相加。表1展示了重编码规则。图2展示了一个乘法运算示例。

图 2 – Radix-4 Booth 算法示例

本设计所需/使用的软件:

• Lattice Diamond设计软件2.0.1版,配合第三方软件Synplify Pro for Lattice和Active-HDL Lattice Edition。

应用

电路构建

Booth Radix-4乘法器的位宽可从4位开始按偶数递增(如6、8、10…),实际使用受限于PLD器件的逻辑密度和运算速度。更大的字长需要更复杂的电路,同时会导致更长的传播延迟。因此较大规模的电路需要采用较低频率的时钟。在MachXO2器件中,6位乘法器测试频率达157MHz,而18位乘法器可运行在140MHz。

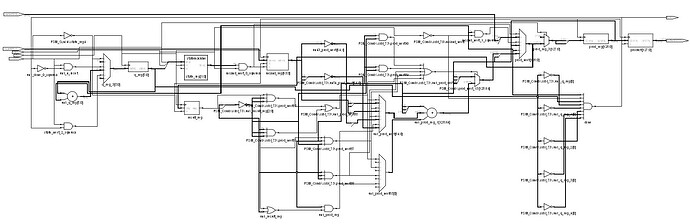

该设计包含五个输入端口(“clk”、“n_reset”、“start”、“mcand"和"mplier”)及两个输出端口(“done"和"product”)。乘法器需要启动脉冲来初始化FSM状态机,加载"mcand"和"mplier"输入值,并使FSM进入"BUSY"工作状态。通过在不同实例间传递"start"和"done"信号,可以实现数学运算步骤的流水线控制。

图3展示了64位实现的RTL结构图。

图 3 - Radix-4 Booth 乘法器 RTL 结构图

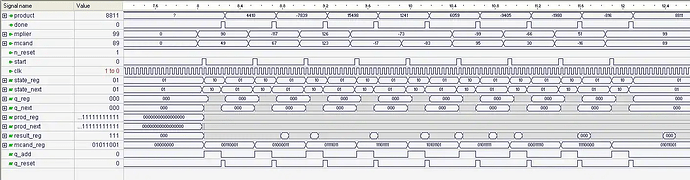

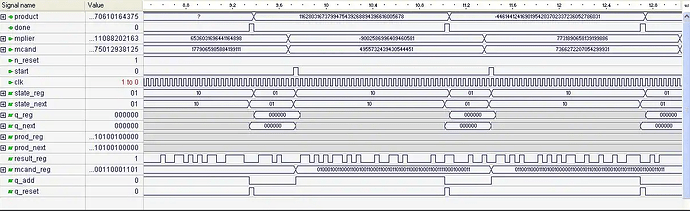

随附的测试平台通过"HDL Diagram"窗口中的"生成测试平台模板"命令创建。阅读Verilog注释可理解"booth_mult_tf.v"文件的具体实现。图4和图5分别展示了8位与64位实现的Aldec Active-HDL波形图。

图 4 - 8 位实现的 Active-HDL 测试平台输出

图 5 - 64 位实现的 Active-HDL 测试平台输出

设计软件

采用Lattice Diamond 2.0.1设计软件开发"booth_mult.v",配合使用Synopsys(Synplify Pro for Lattice)和Aldec(Active-HDL Lattice Edition)工具链。Diamond也可作为独立开发环境,兼容第三方综合与仿真工具。

补充资料

更多设计支持、产品教程、应用指南及用户手册详见Lattice 官网

附录:下载资源

完整Lattice Diamond工程文件下载链接

Booth_mult.v (5.0 KB)

Booth_mult_tf.v (7.1 KB)