# IQ DEMODULATOR

#### FEATURES

- Frequency Range: 1.7 GHz to 2 GHz

- **Integrated Baseband Programmable-Gain** Amplifier

- **On-Chip Programmable Baseband Filter**

- High Cascaded IP3: 21 dBm at 1.9 GHz

- High IP2: 60 dBm at 1.9 GHz

- Hardware and Software Power Down .

- **3-Wire Serial Programmable Interface**

- Single Supply: 4.5-V to 5.5-V Operation

#### **APPLICATIONS**

- Wireless Infrastructure:

- WCDMA

- CDMA

- Wireless Local Loop

- **High-Linearity Direct Downconversion** Receiver

### DESCRIPTION

The TRF3710 is a highly linear and integrated direct-conversion quadrature demodulator optimized for third-generation (3G) wireless infrastructure. The TRF3710 integrates balanced I and Q mixers, LO buffers, and phase splitters to convert an RF signal directly to I and Q baseband. The on-chip programmable-gain amplifiers allow adjustment of the output signal level without the need for external variable-gain (attenuator) devices. The TRF3710 integrates programmable baseband low-pass filters that attenuate nearby interference, eliminating the need for an external baseband filter.

Housed in a 7-mm × 7-mm QFN package, the TRF3710 provides the smallest and most integrated receiver solution available for high-performance equipment.

| PRODUCT | PACKAGE<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKINGS | ORDERING<br>NUMBER | TRANSPORT MEDIA,<br>QUANTITY |

|---------|-----------------|-----------------------|-----------------------------------|---------------------|--------------------|------------------------------|

| TRF3710 | QFN-48          | RGZ                   | –40°C to 85°C                     | TRF3710             | TRF3710IRGZR       | Tape and reel, 2500          |

| 1813710 | QFN-40          | ROZ                   | -40 C 10 85 C                     | 111-3710            | TRF3710IRGZT       | Tape and reel, 500           |

#### **AVAILABLE DEVICE OPTIONS<sup>(1)</sup>**

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI (1) Web site at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

# TRF3710

SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

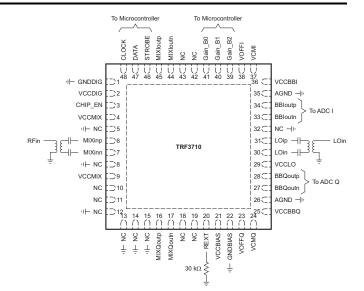

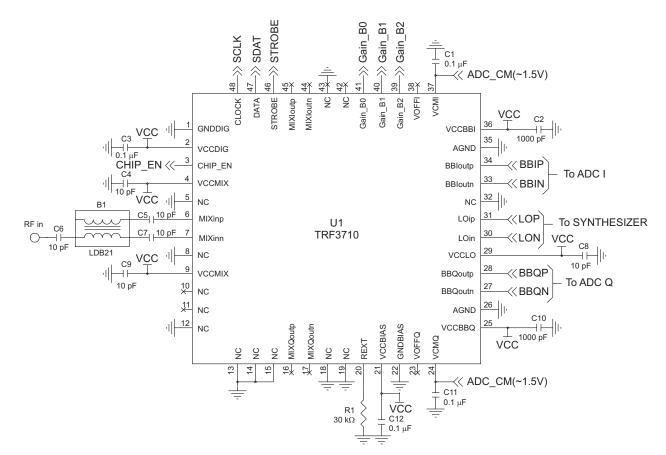

# FUNCTIONAL BLOCK DIAGRAM

2

#### **TERMINAL FUNCTIONS**

| TERMINAL |        |     |                                                                                                                                     |

|----------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.    | I/O | DESCRIPTION                                                                                                                         |

| AGND     | 26, 35 |     | Analog ground; grounds can be tied together.                                                                                        |

| BBloutn  | 33     | 0   | Baseband I output: negative terminal                                                                                                |

| BBloutp  | 34     | 0   | Baseband I output: positive terminal                                                                                                |

| BBQoutn  | 27     | 0   | Baseband Q output: negative terminal                                                                                                |

| BBQoutp  | 28     | 0   | Baseband Q output: positive terminal                                                                                                |

| CHIP_EN  | 3      | I   | Chip enable; enabled = logic level 1, disabled = logic level 0                                                                      |

| CLOCK    | 48     | I   | SPI clock input                                                                                                                     |

| DATA     | 47     | I   | SPI data input (programming data for baseband filter frequency setting, PGA gain settings, and dc offset calibration).              |

| Gain_B0  | 41     | Ι   | PGA fast-gain control bit 0                                                                                                         |

| Gain_B1  | 40     | I   | PGA fast-gain control bit 1                                                                                                         |

| Gain_B2  | 39     | I   | PGA fast-gain control bit 2                                                                                                         |

| GNDBIAS  | 22     |     | Bias-block ground. Grounds can be tied together.                                                                                    |

| GNDDIG   | 1      |     | Digital ground. Grounds can be tied together.                                                                                       |

| LOin     | 30     | I   | Local oscillator input: negative terminal                                                                                           |

| LOip     | 31     | I   | Local oscillator input: positive terminal                                                                                           |

| MIXinn   | 7      | I   | Mixer input: negative terminal, connected to external balanced-to-unbalanced (balun) transformer; balun type is frequency-specific. |

| MIXIoutn | 44     | 0   | Mixer I output: negative terminal (test pin). NC for normal operation                                                               |

| MIXIoutp | 45     | 0   | Mixer I output: positive terminal (test pin). NC for normal operation                                                               |

| MIXinp   | 6      | Ι   | Mixer input: positive terminal, connected to external balun; balun type is frequency-specific.                                      |

| MIXQoutn | 17     | 0   | Mixer Q output: negative terminal (test pin). NC for normal operation                                                               |

| MIXQoutp | 16     | 0   | Mixer Q output: positive terminal (test pin). NC for normal operation                                                               |

| REXT     | 20     | 0   | Reference-bias external resistor: 30 k $\Omega$ ; used to set the bias of internal circuits of chip                                 |

| STROBE   | 46     | I   | SPI enable (latches data into SPI after final clock pulse. Logic level = 1.                                                         |

| VCCBBQ   | 25     |     | Baseband Q-chain power supply, 4.5 V to 5.5 V. Decoupled from other sources                                                         |

| VCCBIAS  | 21     |     | Bias-block power supply, 4.5 V to 5.5 V. Decoupled from other sources                                                               |

| VCCDIG   | 2      |     | Digital power supply, 4.5 V to 5.5 V. Decoupled from other sources                                                                  |

| VCCLO    | 29     |     | Local oscillator power supply, 4.5 V to 5.5 V. Decoupled from other sources                                                         |

| VCCMIX   | 4, 9   |     | Mixer power supply, 4.5 V to 5.5 V. Decoupled from other sources                                                                    |

| VCMQ     | 24     | Ι   | Baseband Q-chain input common mode, nominally 1.5 V                                                                                 |

| VOFFQ    | 23     | I   | Q-chain analog-offset correction input, 0 V to 3 V.                                                                                 |

| VCCBBI   | 36     |     | Baseband I power supply, 4.5 V to 5.5 V. Decoupled from other sources                                                               |

| VCMI     | 37     | I   | Baseband I chain input common mode, nominally 1.5 V                                                                                 |

| VOFFI    | 38     | Ι   | I-chain analog-offset correction input, 0 V to 3 V                                                                                  |

### **THERMAL CHARACTERISTICS**

Over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER <sup>(1)</sup>              | TEST CONDITIONS                            | MIN  | TYP  | MAX  | UNIT |

|-----------------------|---------------------------------------|--------------------------------------------|------|------|------|------|

|                       | Thermal derating innotion to embient  | Soldered slug, no airflow                  |      | 26   |      |      |

| $R_{\theta JA}$       |                                       | Soldered slug, 200-LFM (1,016 m/s) airflow | 20.1 |      | °C/W |      |

|                       | Thermal derating, junction-to-ambient | Soldered slug, 400-LFM (2,032 m/s) airflow |      | 17.4 |      | °C/W |

| $R_{\theta JA}^{(2)}$ |                                       | 7-mm × 7-mm, 48-pin PDFP                   |      | 25   |      |      |

| $R_{\theta JB}$       | Thermal derating, junction-to-board   | 7-mm $\times$ 7-mm, 48-pin PDFP            |      | 12   |      | °C/W |

Determined using JEDEC standard JESD-51 with high-K board 16 layers, high-K board (1)

(2)

SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

#### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

Over operating free-air temperature range (unless otherwise noted)

|                  |                                              | VALUE                         | UNIT |

|------------------|----------------------------------------------|-------------------------------|------|

|                  | Supply voltage range <sup>(2)</sup>          | -0.3 to 5.5                   | V    |

|                  | Digital I/O voltage range                    | –0.3 to V <sub>CC</sub> + 0.5 | V    |

| TJ               | Operating virtual junction temperature range | -40 to 150                    | °C   |

| T <sub>A</sub>   | Operating ambient temperature range          | -40 to 85                     | °C   |

| T <sub>stg</sub> | Storage temperature range                    | -65 to 150                    | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

### **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted)

|                 |                                              | MIN | NOM | MAX | UNIT         |

|-----------------|----------------------------------------------|-----|-----|-----|--------------|

| V <sub>CC</sub> | Power supply voltage                         | 4.5 | 5   | 5.5 | V            |

|                 | Power supply voltage ripple                  |     |     | 940 | $\mu V_{pp}$ |

| T <sub>A</sub>  | Operating ambient temperature range          | -40 |     | 85  | °C           |

| TJ              | Operating virtual junction temperature range | -40 |     | 150 | °C           |

#### **ELECTRICAL CHARACTERISTICS**

Power supply = 5 V, LO = 0 dBm at 25°C (unless otherwise noted)

| PARAMETER          |                                              | TEST CONDITIONS <sup>(1)</sup>                               | MIN   | TYP              | MAX  | UNIT   |

|--------------------|----------------------------------------------|--------------------------------------------------------------|-------|------------------|------|--------|

| DC PAR             | AMETERS                                      |                                                              |       |                  |      |        |

| I <sub>CC</sub>    | Total supply current                         |                                                              |       | 360              |      | mA     |

|                    | Power-down current                           |                                                              |       | 5                |      | mA     |

| IQ DEMO            | DULATOR AND BASEBAND SE                      | CTION                                                        |       |                  |      |        |

| f <sub>RF</sub>    | Frequency range                              |                                                              | 1700  |                  | 2000 | MHz    |

| G <sub>minBB</sub> | Minimum gain                                 |                                                              |       |                  | 20   | dB     |

| G <sub>maxBB</sub> | Maximum gain                                 |                                                              |       | 43               | 45   | dB     |

|                    | Gain range                                   |                                                              | 22    | 24               |      | dB     |

|                    | Gain step                                    |                                                              |       | 1 <sup>(2)</sup> |      | dB     |

| $NF_BB$            | Noise figure                                 | Gain setting = 15                                            |       | 13.5             | 14.5 | dB     |

| IIP3 <sub>BB</sub> | Third-order input intercept point            | Gain setting = 15 $^{(3)}$ $^{(4)}$                          |       | 21               |      | dBm    |

| OIP3 <sub>BB</sub> | Output third intercept point                 | Gain setting = 15; two tones, 1 $V_{PP}$ each <sup>(5)</sup> |       | 32               |      | dBVrms |

| OIP1 <sub>BB</sub> | Output compression point                     | One tone <sup>(6)</sup>                                      |       | 3                |      | dBVrms |

| IIP2 <sub>BB</sub> | Second-order input intercept point           | Gain setting = $15^{(7)}$                                    |       | 60               |      | dBm    |

| f <sub>LPF</sub>   | Baseband low-pass filter cutoff<br>frequency | 1-dB point <sup>(8)</sup>                                    | 0.615 |                  | 1.92 | MHz    |

(1) Balun used for measurements: Band 1: 1700-MHz balun = Murata LDB211G8005C-001; Band 2: 1800- to 1900-MHz balun = Murata LDB211G9005C-001

- (2) Between two consecutive gain settings

- (3) Two CW tones of -30 dBm at ±900-kHz and ±1.7-MHz offset (baseband filter 1-dB cutoff frequency of minimum LPF).

- (4) Two CW tones of -30 dBm at ±2.7-MHz and ±5.9-MHz offset (baseband filter 1-dB cutoff frequency of maximum LPF).

- (5) Two CW tones at an offset from LO frequency smaller than the baseband filter cutoff frequency.

- (6) Single CW tone at an offset from LO smaller than the baseband filter cutoff frequency.

- (7) Two tones at  $f_{RF1} = f_{LO} \pm 900$  kHz and  $f_{RF2} = f_{LO} \pm 1$  MHz; IM<sub>2</sub> product measured at 100-kHz output frequency (for minimum baseband filter 1-dB cutoff frequency). The two tones are at  $f_{RF1} = f_{LO} \pm 2.7$  MHz and  $f_{RF2} = f_{LO} \pm 2.8$  MHz, and the IM<sub>2</sub> product measured at 100-kHz output frequency (for maximum baseband filter 1-dB cutoff frequency).

- (8) Baseband low-pass filter 1-dB cutoff frequency is programmable through SPI between minimum and maximum values.

### **ELECTRICAL CHARACTERISTICS (continued)**

Power supply = 5 V, LO = 0 dBm at 25°C (unless otherwise noted)

|                 | PARAMETER                                         | TEST CONDITIONS <sup>(1)</sup>                        | MIN                 | TYP | MAX                 | UNIT    |

|-----------------|---------------------------------------------------|-------------------------------------------------------|---------------------|-----|---------------------|---------|

|                 |                                                   | 615 kHz                                               |                     |     | 1                   |         |

|                 | Baseband relative attenuation                     | 900 kHz                                               |                     | 10  |                     |         |

|                 | at minimum LPF cutoff                             | 1.7 MHz                                               |                     | 50  |                     | dB      |

|                 | frequency <sup>(9)</sup>                          | 5 MHz                                                 | 60                  |     |                     |         |

|                 |                                                   | 20 MHz                                                |                     | 100 |                     |         |

|                 |                                                   | 1.92 MHz                                              |                     |     | 1                   |         |

|                 | Baseband relative attenuation                     | 2.7 MHz                                               |                     | 10  |                     | 15      |

|                 | at maximum LPF cutoff<br>frequency <sup>(9)</sup> | 5 MHz                                                 |                     | 50  |                     | dB      |

|                 |                                                   | 20 MHz                                                |                     | 100 |                     | 1       |

|                 | Baseband filter phase linearity                   | RMS phase deviation from linear phase <sup>(10)</sup> |                     | 1.8 |                     | Degrees |

|                 | Baseband filter amplitude ripple                  | See (10)                                              |                     | 0.5 |                     | dB      |

|                 | Sideband suppression                              |                                                       | 35                  |     |                     | dB      |

|                 | Output load impedance                             | Parallel resistance                                   |                     | 1   |                     | kΩ      |

|                 |                                                   | Parallel capacitance                                  |                     | 20  |                     | pF      |

| V <sub>CM</sub> | Output common mode                                | Measured at I and Q channel baseband outputs          | 0.7                 | 1.5 | 4                   | V       |

| LOCAL           | OSCILLATOR PARAMETERS                             |                                                       |                     |     |                     |         |

|                 | Local oscillator frequency                        |                                                       | 1700                |     | 2000                | MHz     |

|                 | LO input level                                    |                                                       |                     | 0   |                     | dBm     |

|                 | LO leakage                                        | At MIXinn/p                                           |                     |     | -58                 | dBm     |

| DIGITA          | L INTERFACE                                       |                                                       |                     |     |                     |         |

| VIH             | High-level input voltage                          |                                                       | 2                   | 5   | V <sub>CC</sub>     | V       |

| V <sub>IL</sub> | Low-level input voltage                           |                                                       | 0                   |     | 0.8                 | V       |

| V <sub>OH</sub> | High-level output voltage                         |                                                       | 0.8 V <sub>CC</sub> |     |                     | V       |

| V <sub>OL</sub> | Low-level output voltage                          |                                                       |                     |     | 0.2 V <sub>CC</sub> | V       |

(9) Attenuation relative to passband gain

(10) Across-filter passband: 615 kHz (minimum baseband filter cutoff frequency) and 1.92 MHz (maximum baseband filter cutoff frequency).

SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

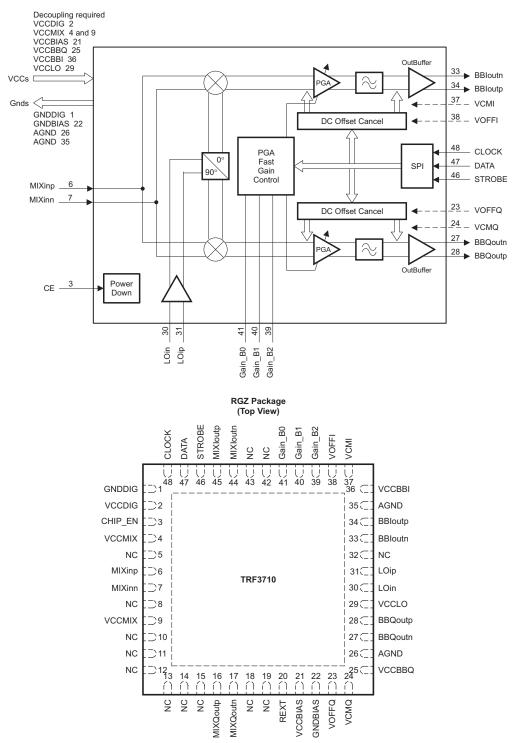

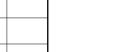

#### TIMING REQUIREMENTS

Power supply = 5 V, LO = 0 dBm at 25°C (unless otherwise noted)

|                    | PARAMETER           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|---------------------|-----------------|-----|-----|-----|------|

| t <sub>(CLK)</sub> | Clock period        |                 | 50  |     |     | ns   |

| t <sub>su1</sub>   | Setup time, data    |                 | 10  |     |     | ns   |

| t <sub>h</sub>     | Hold time, data     |                 | 10  |     |     | ns   |

| t <sub>w</sub>     | Pulse width, STROBE |                 | 20  |     |     | ns   |

| t <sub>su2</sub>   | Setup time, STROBE  |                 | 10  |     |     | ns   |

Figure 1. Serial Programming Timing

6

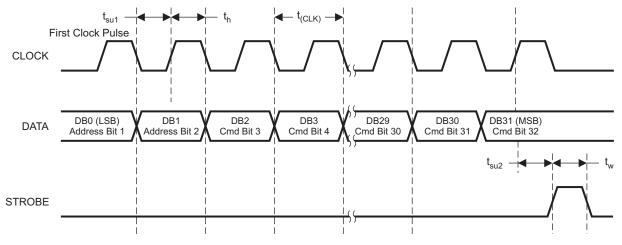

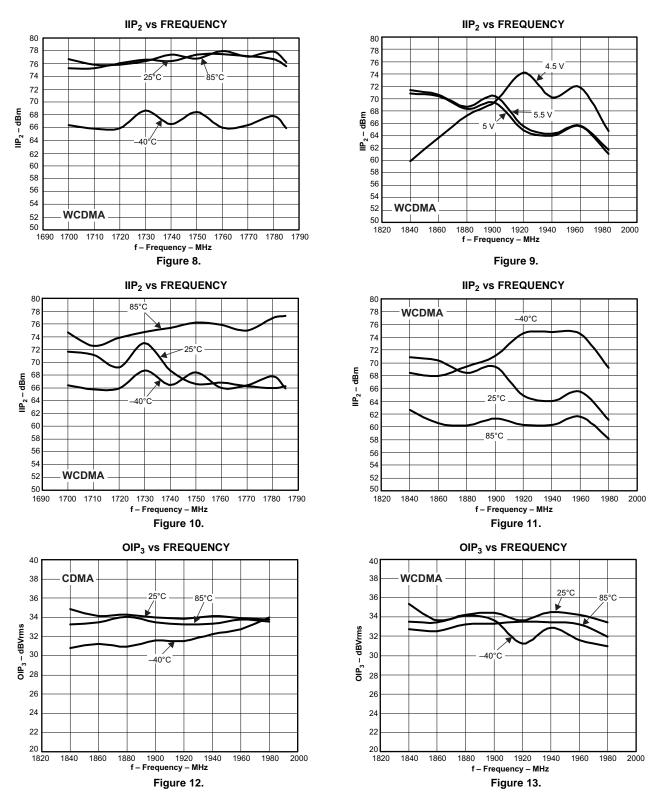

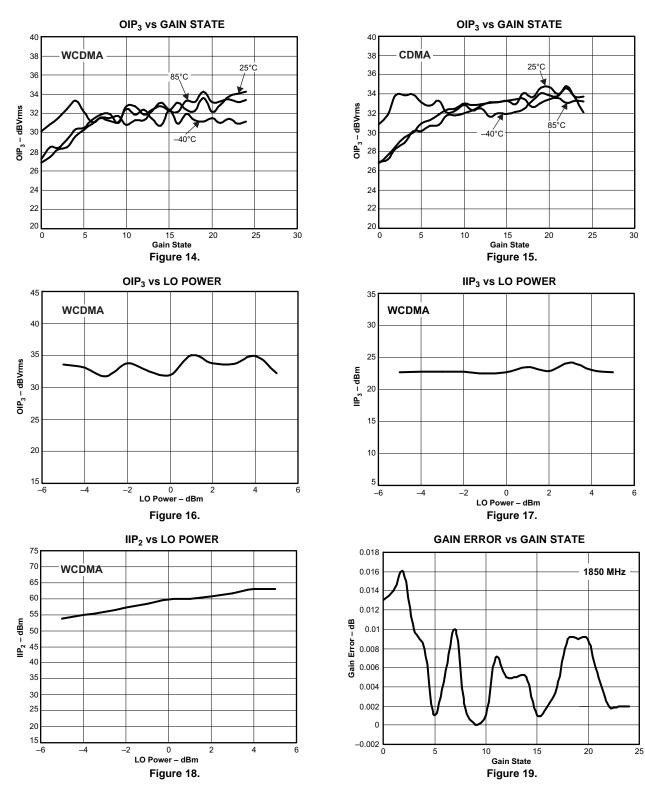

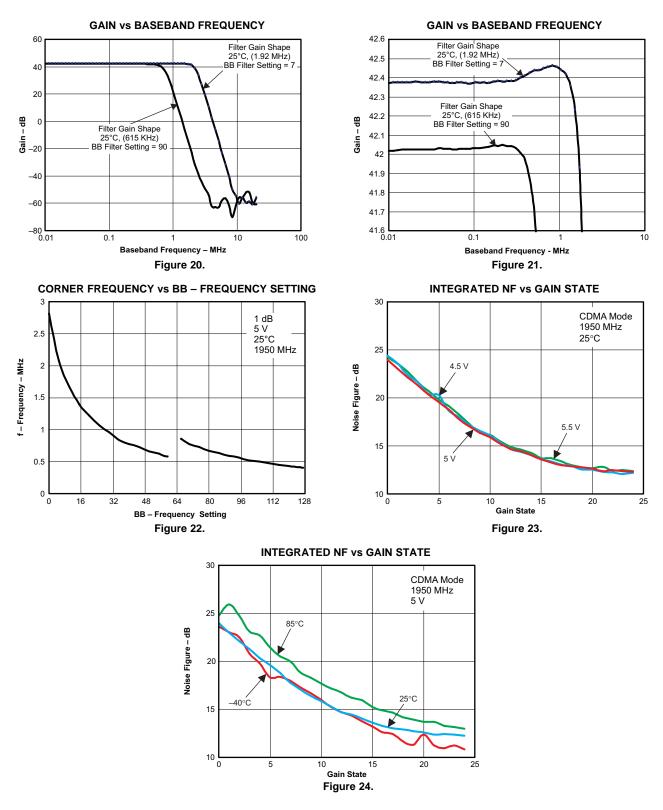

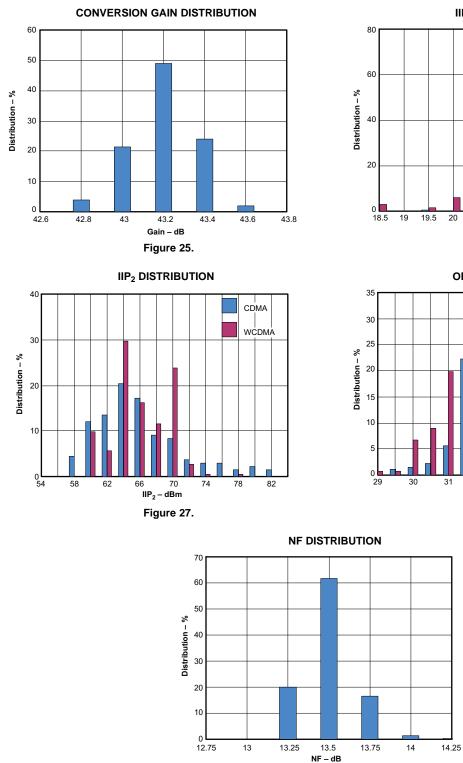

#### **TYPICAL CHARACTERISTICS**

$V_{CC} = 5 \text{ V}, \text{ } T_A = 25^{\circ}\text{C}, 1950 \text{ MHz}, \text{ gain setting} = 24 \text{ (unless otherwise stated)}.$ (CDMA = *BBFREQ* = 90, WCDMA = *BBFREQ* = 7)

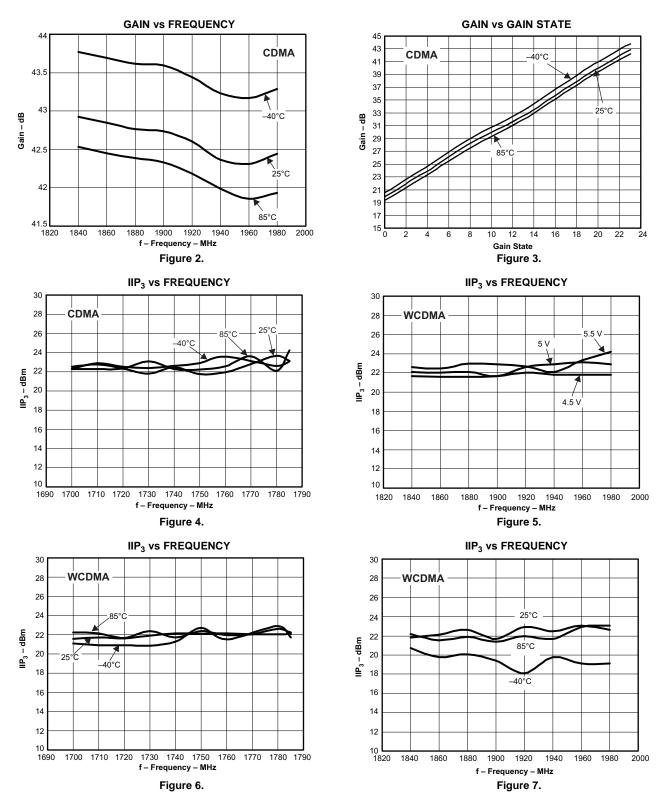

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CC} = 5 \text{ V}, \text{ } \text{T}_{A} = 25^{\circ}\text{C}, 1950 \text{ MHz}, \text{ gain setting} = 24 \text{ (unless otherwise stated)}.$ (CDMA = *BBFREQ* = 90, WCDMA = *BBFREQ* = 7)

# **TYPICAL CHARACTERISTICS (continued)**

$V_{CC} = 5 \text{ V}, \text{ } \text{T}_{A} = 25^{\circ}\text{C}, 1950 \text{ MHz}, \text{ gain setting} = 24 \text{ (unless otherwise stated)}.$ (CDMA = *BBFREQ* = 90, WCDMA = *BBFREQ* = 7)

9

### **TYPICAL CHARACTERISTICS (continued)**

$V_{CC} = 5 \text{ V}, \text{ } \text{T}_{A} = 25^{\circ}\text{C}, 1950 \text{ MHz}, \text{ gain setting} = 24 \text{ (unless otherwise stated)}.$ (CDMA = *BBFREQ* = 90, WCDMA = *BBFREQ* = 7)

CDMA

сома

wcdma

35

36

WCDMA

**IIP3 DISTRIBUTION**

20.5 21 21.5 22 22.5 23

IIP3 – dBm

Figure 26.

**OIP3 DISTRIBUTION**

# **TYPICAL CHARACTERISTICS**

#### **HISTOGRAM PLOTS**

32

OIP<sub>3</sub> – dBVrms

Figure 28.

33

34

Figure 29.

SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

#### SERIAL INTERFACE PROGRAMMING REGISTERS DEFINITION

The TRF3710 features a 3-wire serial programming interface (SPI) that controls an internal 32-bit shift register. There are a total of three signals that must be applied: CLOCK (pin 48), serial DATA (pin 47), and STROBE (pin 46). DATA (DB0–DB31) is loaded LSB-first and is read on the rising edge of the CLOCK. STROBE is asynchronous to CLOCK, and at its rising edge, the data in the shift register are loaded onto the selected internal register. The first two bits (DB0–DB1) are the address to select the available internal registers. Figure 30 shows the serial interface timing for the TRF3710.

|                    | PARAMETER           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|---------------------|-----------------|-----|-----|-----|------|

| t <sub>(CLK)</sub> | Clock period        |                 | 50  |     |     | ns   |

| t <sub>su1</sub>   | Setup time, data    |                 | 10  |     |     | ns   |

| t <sub>h</sub>     | Hold time, data     |                 | 10  |     |     | ns   |

| t <sub>w</sub>     | Pulse width, STROBE |                 | 20  |     |     | ns   |

| t <sub>su2</sub>   | Setup time, STROBE  |                 | 10  |     |     | ns   |

| Figure 3 | 30. \$ | Serial | Interface | Timing |

|----------|--------|--------|-----------|--------|

|----------|--------|--------|-----------|--------|

#### SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

#### **Register 0**

| Register | Address | PWD<br>Mixer | PWD<br>LO Buff | PWD<br>Test<br>Buff | PWD<br>Filter | PWD<br>Output<br>Buff | RSVD  | PWD<br>Dig Cal<br>Block | PWD<br>Ana<br>Cal<br>Block |       | Baseba | ind Gain S | setting      |       | BB<br>Freq<br>Cutoff<br>Set |

|----------|---------|--------------|----------------|---------------------|---------------|-----------------------|-------|-------------------------|----------------------------|-------|--------|------------|--------------|-------|-----------------------------|

| Bit0     | Bit1    | Bit2         | Bit3           | Bit4                | Bit5          | Bit6                  | Bit7  | Bit8                    | Bit9                       | Bit10 | Bit11  | Bit12      | Bit13        | Bit14 | Bit15                       |

|          | Baseba  | nd Freq C    | utoff Settir   | ngs Cont.           |               | R                     | SVD   | -                       | Detector<br>dwidth         |       | RSVD   |            | Cal<br>Reset | Spare | Spare                       |

| Bit16    | Bit17   | Bit18        | Bit19          | Bit20               | Bit21         | Bit22                 | Bit23 | Bit24                   | Bit25                      | Bit26 | Bit27  | Bit28      | Bit29        | Bit30 | Bit31                       |

#### Figure 31. Register 0 Map

#### Table 1. Register 0: Device Setup

| REGISTER 0 | NAME              | RESET<br>VALUE | WORKING DESCRIPTION                                                                                                                                                                 |

|------------|-------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit0       | ADDR_0            | 0              | Address bits                                                                                                                                                                        |

| Bit1       | ADDR_1            | 0              | Address bits                                                                                                                                                                        |

| Bit2       | PWD_MIX           | 0              | Mixer power down (off = 1)                                                                                                                                                          |

| Bit3       | PWD_LO            | 0              | LO buffer power down (off = 1)                                                                                                                                                      |

| Bit4       | PWD_BUF1          | 1              | Test buffer power down (off = 1)                                                                                                                                                    |

| Bit5       | PWD_FILT          | 0              | Baseband filter power down (off = 1)                                                                                                                                                |

| Bit6       | PWD_BUF2          | 0              | Output buffer power down (off = 1)                                                                                                                                                  |

| Bit7       | Reserved          | 0              |                                                                                                                                                                                     |

| Bit8       | PWD_DC_OFF_DIG    | 1              | Digital calibration blocks power down (off = 1)                                                                                                                                     |

| Bit9       | PWD_DC_OFF_ANA    | 1              | Analog calibration blocks power down (off = 1)                                                                                                                                      |

| Bit10      | BBGAIN_0          | 1              | Sets baseband gain: the default power-on BBGAIN setting = 15 (corresponding to a                                                                                                    |

| Bit11      | BBGAIN_1          | 1              | typical gain of 34 dB). There are 25 gain settings (0 to 24) in 1-dB increments. For a                                                                                              |

| Bit12      | BBGAIN_2          | 1              | desired device gain, the <i>BBGAIN</i> setting is determined by the following equation:<br><i>BBGAIN</i> setting = $24 - [(typical device gain at BBGAIN = 24) - (desired device)]$ |

| Bit13      | BBGAIN_3          | 1              | gain)]. For example, for a desired device gain of 27 dB, the BBGAIN setting would                                                                                                   |

| Bit14      | BBGAIN_4          | 0              | be 24 − (43 − 27) = 8, which is bits 14−10 <0 1000>.                                                                                                                                |

| Bit15      | BBFREQ_0          | 1              |                                                                                                                                                                                     |

| Bit16      | BBFREQ_1          | 0              |                                                                                                                                                                                     |

| Bit17      | BBFREQ_2          | 1              | Sets BB frequency cutoff; default = 85. Example: For CDMA, the corner frequency is                                                                                                  |

| Bit18      | BBFREQ_3          | 0              | 615 kHz. See the 1-dB corner frequency vs. frequency setting plot Figure 22 to determine the setting, which is 90. Then set bit 15 through bit 21 to <101 1010>,                    |

| Bit19      | BBFREQ_4          | 1              | which corresponds to 90.                                                                                                                                                            |

| Bit20      | BBFREQ_5          | 0              |                                                                                                                                                                                     |

| Bit21      | BBFREQ_6          | 1              |                                                                                                                                                                                     |

| Bit22      | Reserved          | 1              |                                                                                                                                                                                     |

| Bit23      | Reserved          | 0              |                                                                                                                                                                                     |

| Bit24      | EN_FLT_B0         | 0              |                                                                                                                                                                                     |

| Bit25      | EN_FLT_B1         | 0              | DC detector bandwidth                                                                                                                                                               |

| Bit26      | Reserved          | 0              |                                                                                                                                                                                     |

| Bit27      | Internal use only | 0              |                                                                                                                                                                                     |

| Bit28      | Internal use only | 0              |                                                                                                                                                                                     |

| Bit29      | CAL_RESET         | 0              | Reset the internal calibration logic when = 1.                                                                                                                                      |

| Bit30      | Spare0            | 0              |                                                                                                                                                                                     |

| Bit31      | Spare1            | 0              |                                                                                                                                                                                     |

- **Baseband PGA gain:** *BBGAIN\_*[4:0] (B[14:10]) sets the gain of the baseband programmable gain amplifier. The acceptable values are from <0 0000> to <1 1000>. (See the *Gain Control* section for more information.)

- **Baseband filter cutoff frequency:** *BBFREQ\_*[6:0] (B[21:15]) controls the baseband 1-dB cutoff frequency. An all-0s word sets the filter to its maximum cutoff frequency, whereas an all-1s word corresponds to minimum filter bandwidth.

- **EN\_FLT\_B[0:1]:** These bits control the bandwidth of the detector used to measure the dc offset during the automatic calibration. There is an RC filter in front of the detector that can be fully bypassed. *EN\_FLT\_B0* controls the resistor (bypass = 1), while *EN\_FLT\_B1* controls the capacitor (bypass = 1). The typical 3-dB cutoff frequencies of the detector bandwidth are summarized in Table 2 (see the *Application Information* section for more detail on the dc offset calibration and the detector bandwidth).

| EN_FLT_B1 | EN_FLT_B0 | Typical 3-dB Cutoff<br>Frequency | Notes                          |  |  |  |  |

|-----------|-----------|----------------------------------|--------------------------------|--|--|--|--|

| Х         | 0         | 10 MHz                           | Maximum bandwidth; bypass R, C |  |  |  |  |

| 0         | 1         | 10 kHz                           | Enable R                       |  |  |  |  |

| 1         | 1         | 1 kHz                            | Minimum bandwidth; enable R, C |  |  |  |  |

#### **Table 2. Typical Cutoff Frequencies**

#### **Register 1**

| Register | Address | Autocal | Enable<br>Autocal | DAC Bits to Be Set During Manual Cal I/O |                                  |         |                                     |               |         |                        |         |                   |          |            |         |

|----------|---------|---------|-------------------|------------------------------------------|----------------------------------|---------|-------------------------------------|---------------|---------|------------------------|---------|-------------------|----------|------------|---------|

| Bit0     | Bit1    | Bit2    | Bit3              | Bit4                                     | Bit5                             | Bit6    | Bit7                                | Bit8          | Bit9    | Bit10                  | Bit11   | Bit12             | Bit13    | Bit14      | Bit15   |

| DAC B    |         | ts CONT |                   | Cal. Re                                  | et Digital<br>solution<br>hannel | Cal. Re | set Digital<br>esolution<br>Channel | Bin<br>Search | Divisio | on Ratio fo<br>Divider | r Clock | Cal Clk<br>Select | Internal | Osc Freq 1 | rimming |

| Bit16    | Bit17   | Bit18   | Bit19             | Bit20                                    | Bit21                            | Bit22   | Bit23                               | Bit24         | Bit25   | Bit26                  | Bit27   | Bit28             | Bit29    | Bit30      | Bit31   |

### Figure 32. Register 1 Map

#### Table 3. Register 1: Device Setup

| REGISTER 1  | NAME           | RESET<br>VALUE | WORKING DESCRIPTION                                                                                  |  |  |  |  |  |

|-------------|----------------|----------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit0        | ADDR_0         | 1              | Address bits                                                                                         |  |  |  |  |  |

| Bit1        | ADDR_1         | 0              | Address bits                                                                                         |  |  |  |  |  |

| Bit2        | AUTO_CAL       | 1              | Auto dc offset correction when = 1; otherwise manual                                                 |  |  |  |  |  |

| Bit3        | EN_AUTOCAL     | 0              | Autocalibration begins when bit = 1. This bit is reset after calibration completes.                  |  |  |  |  |  |

| Bit4        | IDAC_BIT0      | 0              |                                                                                                      |  |  |  |  |  |

| Bit5        | IDAC_BIT1      | 0              |                                                                                                      |  |  |  |  |  |

| Bit6        | IDAC_BIT2      | 0              |                                                                                                      |  |  |  |  |  |

| Bit7        | IDAC_BIT3      | 0              |                                                                                                      |  |  |  |  |  |

| Bit8        | IDAC_BIT4      | 0              |                                                                                                      |  |  |  |  |  |

| Bit9        | IDAC_BIT5      | 0              |                                                                                                      |  |  |  |  |  |

| Bit10       | IDAC_BIT6      | 0              |                                                                                                      |  |  |  |  |  |

| Bit11       | IDAC_BIT7      | 1              | DAC bits to be set during manual cal I/Q                                                             |  |  |  |  |  |

| Bit12       | QDAC_BIT0      | 0              | DAC bits to be set during mandal car i/Q                                                             |  |  |  |  |  |

| Bit13       | QDAC_BIT1      | 0              |                                                                                                      |  |  |  |  |  |

| Bit14 QDAC_ | QDAC_BIT2      | 0              |                                                                                                      |  |  |  |  |  |

| Bit15       | QDAC_BIT3      | 0              |                                                                                                      |  |  |  |  |  |

| Bit16       | QDAC_BIT4      | 0              |                                                                                                      |  |  |  |  |  |

| Bit17       | QDAC_BIT5      | 0              |                                                                                                      |  |  |  |  |  |

| Bit18       | QDAC_BIT6      | 0              |                                                                                                      |  |  |  |  |  |

| Bit19       | QDAC_BIT7      | 1              |                                                                                                      |  |  |  |  |  |

| Bit20       | IDET_B0        | 1              | Set the dc offset digital calibration resolution for I channel.                                      |  |  |  |  |  |

| Bit21       | IDET_B1        | 1              |                                                                                                      |  |  |  |  |  |

| Bit22       | QDET_B0        | 1              | Set the dc offset digital calibration resolution for Q channel.                                      |  |  |  |  |  |

| Bit23       | QDET_B1        | 1              |                                                                                                      |  |  |  |  |  |

| Bit24       | Bin Search     | 1              | Set to 1 for autocalibration; set to 0 for manual control.                                           |  |  |  |  |  |

| Bit25       | CLK_DIV_RATIO0 | 0              |                                                                                                      |  |  |  |  |  |

| Bit26       | CLK_DIV_RATIO1 | 0              | DC offset autocalibration clock divider:<br>division ratios = 1, 8, 16, 128, 256, 1024, 2048, 16,684 |  |  |  |  |  |

| Bit27       | CLK_DIV_RATIO2 | 0              | · · · · · · · · · · · · · · · · · · ·                                                                |  |  |  |  |  |

| Bit28       | CAL_CLK_SEL    | 1              | Select internal oscillator when 1; select SPI clock when 0.                                          |  |  |  |  |  |

| Bit29       | OSC_TRIM0      | 1              | Internal oscillator frequency trimming                                                               |  |  |  |  |  |

| Bit30       | OSC_TRIM1      | 1              | 000 → 300 kHz                                                                                        |  |  |  |  |  |

| Bit31       | OSC_TRIM2      | 0              | 111 → 1.8 MHz                                                                                        |  |  |  |  |  |

SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

- AUTO\_CAL (Bit2): When 1, the dc offset autocalibration is selected.

- **EN\_AUTOCAL (Bit3):** Setting this bit to 1 starts the dc offset autocalibration. At the end of the calibration, the bit is reset to 0 (see the *Application Information* section for more details on dc offset correction).

- *IDET\_B*[1:0], *QDET\_B*[1:0]: These bits control the maximum output dc voltage of the dc-offset correction DAC (I and Q channels).

- **CLK\_DIV\_RATIO[2:0]:** Frequency divider for the calibration clock. The incoming clock (either the serial interface clock or the internal oscillator) divided by the divider ratio set by bits 25–27, generates the reference clock used during the autocalibration.

- CAL\_CLK\_SEL: Selects the internal oscillator or the external SPI clock as calibration clock

- **OSC\_TRIM**[2:0]: Bits 29–31 control the internal oscillator frequency.

### **APPLICATION INFORMATION**

#### **GAIN CONTROL**

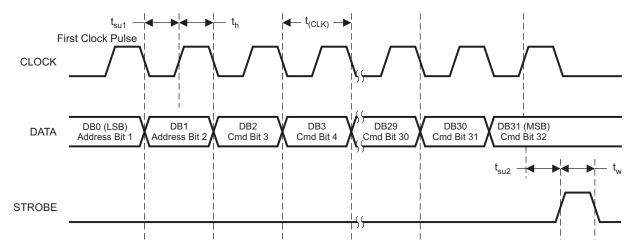

The TRF3710 integrates a baseband programmable-gain amplifier (PGA) that provides 24 dB of gain range with 1-dB steps. The PGA gain is controlled through SPI by a 5-bit word (register 0, bits 10–14). Alternatively, the PGA can be programmed by a combination of 5 bits programmed through the SPI and three parallel external bits (pins Gain\_B2, Gain\_B1, Gain\_B0). The parallel bits allow a fast gain change (0 db to 7 dB by 1-dB steps) without the need to reprogram the SPI registers.

The PGA gain control word (*BBGAIN*[0:4]) can be programmed to a setting between 0 and 24. This word is the sum of the SPI programmed gain (register 0, bits 10–14) and the parallel external 3 bits as shown in Figure 33. Setting the PGA gain setting above 24 is not valid. Typical applications set the PGA gain to 15, which allows room to adjust the PGA gain up or down to maintain desired output signal to the analog-to-digital converter over all conditions.

From External Pins

Figure 33. PGA Gain Control Word

For example, if a PGA gain setting of 20 dB is desired, then the SPI can be programmed directly to 20. Alternatively, the SPI gain register can be programmed to 15 and the parallel external bits set to 101 (binary), corresponding to an additional 5 dB.

#### AUTOMATED DC OFFSET CALIBRATION

The TRF3710 provides an automatic calibration procedure for adjusting the dc offset in the baseband I/Q paths. The digital dc offset correction is engaged by setting the *PWD\_DC\_OFF\_DIG* (register 0, bit 8) to 0 and the *PWD\_DC\_OFF\_ANA* (register 0, bit 9) to 1. The internal calibration requires a clock in order to function. TRF3710 can use the internal relaxation oscillator or the external SPI clock. Using the internal oscillator is the preferred method. Selecte the internal oscillator by setting the Cal\_Sel\_Clk (register 1, bit 28) to 1. The internal oscillator is detailed in Table 4.

| OSC_TRIM1 | OSC_TRIM0                                                        | Frequency                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0         | 0                                                                | 300 kHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 0         | 1                                                                | 500 kHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 1         | 0                                                                | 700 kHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 1         | 1                                                                | 900 kHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 0         | 0                                                                | 1.1 MHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 0         | 1                                                                | 1.3 MHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 1         | 0                                                                | 1.5 MHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 1         | 1                                                                | 1.8 MHz                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|           | OSC_TRIM1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | OSC_TRIM1         OSC_TRIM0           0         0           0         1           1         0           1         1           0         0           1         1           0         0           1         1           0         0           1         1           0         0           1         0           1         1           1         1 |  |  |  |  |  |  |  |

| Table 4. | Internal | Oscillator | Frequency | <b>Control</b> |

|----------|----------|------------|-----------|----------------|

|          |          |            |           |                |

The default setting of these registers corresponds to 900-kHz oscillator frequency; this setting is sufficient for autocalibration and does not need to be modified.

SLWS199A-AUGUST 2007-REVISED FEBRUARY 2008

The internal dc offset correction DACs output full scale range is programmable (*IDET\_B*[0:1] and *QDET\_B*[0:1], register 1, bits 20–23). The range is shown in Table 5.

# Table 5. DC Offset Correction DAC Programmable Range

| I(Q)DET_B1 | I(Q)DET_B0 | Full Scale |

|------------|------------|------------|

| 0          | 0          | 10 mV      |

| 0          | 1          | 20 mV      |

| 1          | 0          | 30 mV      |

| 1          | 1          | 40 mV      |

The maximum dc offset correction range can be calculating by multiplying the values in Table 5 by the baseband PGA gain. The LSB of the digital correction depends on the programmed maximum correction range. For optimum resolution and best correction, the dc offset DAC range should be set to 10 mV for both the I and Q channels with the PGA gain set for the nominal condition. The output of the dc-offset-correction DAC is affected by a change in the PGA gain, but if the initial calibration yields optimum results, then the adjustment of the PGA gain during normal operation does not significantly impair the dc offset balance. For example, if the optimized calibration yields a dc offset balance of 2 mV at a gain setting of 17, then the dc offset maintains less than 10-mV balance as the gain is adjusted  $\pm 7$  dB.

The dc offset correction DACs are programmed from the internal registers when the *AUTO\_CAL* bit (register 1, bit 2) is set to 1. At start-up, the internal registers are loaded at half-scale, corresponding to a decimal value of 128. When an autocalibration is desired, verify that the *Bin\_Search* bit (register 1, bit 24) is set to 1. Initiate the autocalibration process by toggling the *EN\_AUTOCAL* bit (register 1, bit 3) to 1. When the calibration is over, this bit is automatically reset to 0. During calibration, the RF local oscillator must be applied.

At each clock cycle during an autocalibration sequence, the internal circuitry senses the output dc offset and calculates the new dc current for the DAC. After the ninth clock cycle, the calibration is complete and the *AUTO\_CAL* bit is reset to 0. The dc offset DAC state is stored in the internal registers and maintained as long as the power supply is kept on, or until the *Cal Reset* (register 1, bit 29) is toggled to 1 or a new calibration is started.

The required clock speed for the optimum calibration is determined by the internal detector behavior (integration bandwidth, gain, sensitivity). The input bandwidth of the detector can be adjusted by changing the cutoff frequency of the RC low-pass filter in front of the detector (register 0, bits 24–25), corresponding to 3-dB corner-frequency steps of 10 MHz, 10 kHz, and 1 kHz. The speed of the clock can be slowed down by selecting a clock divider ratio (register 1, bits 25–27).

The detector has more averaging time the slower the clock; therefore, it can be desirable to slow down the clock speed for a given condition to achieve optimum results. For example, if there is no RF present on the RF input port, the detection filter can be left wide (10 MHz) and the clock divider can be left at div-by-1. The autocalibration yields a dc offset balance between the differential baseband output ports (I and Q) that is less than 15 mV. Some minor improvement may be obtained by increasing the averaging of the detector by increasing the clock divider up to 256.

However, if there is a modulated RF signal present at the input port, it is desirable to reduce the detector bandwidth to filter out most of the modulated signal. The detector bandwidth can be set to a 1-kHz corner frequency. With the modulated signal present, and with the detection bandwidth reduced, additional averaging is required to get optimum results. A clock divider setting of 1024 yields optimum results.

An increase in the averaging is possible by increasing the clock divider at the expense of longer converging time. The convergence time can be calculated by the following:

$$\pi_{C} = \frac{(Auto\_Cal\_Clk\_Cycles) \times (Clk\_Divider)}{Osc Freq}$$

(1)

With a clock divider of 1024 and with the nominal oscillator frequency of 900 kHz, the convergence time is:

$$\tau_{\rm C} = \frac{(9) \times (1024)}{900 \text{ kHz}} = 10.24 \text{ ms}$$

(2)

#### ALTERNATE METHOD FOR ADJUSTING DC OFFSET

The internal registers controlling the internal dc current DAC are accessible through the SPI, providing a user-programmable method for implementing the dc offset calibration. To employ this option, the *Auto Cal* bit must be set to 0 and the *Bin\_Search* set to 0. During this calibration, an external instrument monitors the output dc offset between the I/Q differential outputs and programs the internal registers (*IDAC\_BIT*[0:7] and *QDAC\_BIT*[0:7] bits, register 1, bits 4–19) to cancel the dc offset.

The TRF3710 also offers a third dc offset calibration option to control the output dc offset by an external voltage (0–3 V) injected at the VOFFI and VOFFQ pins. Set *PWD\_DC\_OFF\_DIG* (register 0, bit 8) to 1 (Off) and set *PWD\_DC\_OFF\_ANA* (register 0, bit 9) to 0 to engage the external analog voltage control of the output dc offset. The analog voltage at the VOFFI and VOFFQ pins can be adjusted to provide the proper dc offset balance.

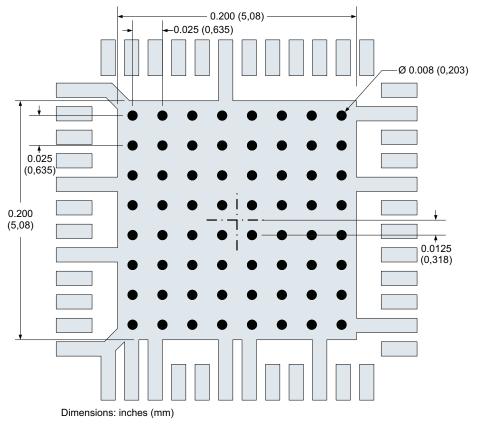

#### PCB LAYOUT GUIDELINES

The TRF3710 device is designed with a ground slug on the back of the package that must be soldered to the printed-circuit board (PCB) ground with adequate ground vias to ensure a good thermal and electrical connection. The recommended via pattern and ground pad dimensions are shown in Figure 34. The recommended via diameter is 8 mils (0.203 mm). The ground pins of the device can be directly tied to the ground slug pad for a low-inductance path to ground. Additional ground vias may be added if space allows. The NC (no connect) pins can also be tied to the ground plane.

Decoupling capacitors at each of the supply pins is recommended. The high-frequency decoupling capacitors for the RF mixers (VCCMIX) should be placed close to the respective pins. The value of the capacitor should be chosen to provide a low impedance RF path to ground at the frequency of operation. Typically, this value is around 10 pF or lower. The other decoupling capacitors at the other supply pins should be kept as close to the respective pins as possible.

The device exhibits symmetry with respect to the quadrature output paths. It is recommended that the PCB layout maintain that symmetry in order to ensure the quadrature balance of the device is not impaired. The I/Q output traces should be routed as differential pairs and the lengths all kept equal to each other. Decoupling capacitors for the supply pins should be kept symmetrical where possible. The RF differential input lines related to the RF input and the LO input should also be routed as differential lines with the respective lengths kept equal. If an RF balun is used to convert a single-ended input to a differential input, then the RF balun should be placed close to the device. Implement the RF balun layout according to the manufacturer's guidelines to provide best gain and phase balance to the differential outputs. On the RF traces, maintain proper trace widths to keep the characteristic impedance of the RF traces at a nominal 50  $\Omega$ .

Figure 34. PCB Layout Guidelines

#### **APPLICATION SCHEMATICS**

The typical application schematic is shown in Figure 35. The RF bypass capacitors and coupling capacitors are depicted with 10-pF capacitors. These values can be adjusted to provide the best high-frequency bypass based on the frequency of operation.

The RF input port and the RF LO port require differential input paths. Single-ended RF inputs to these ports can be converted with an RF balun that is centered on the band of interest. Linearity performance of the TRF3710 depends on the amplitude and phase balance of the RF balun; therefore, care should be taken with the selection of the balun device and with the RF layout of the device. The recommended RF balun devices are listed in Table 6.

| MANUFACTURER | PART NUMBER      | FREQUENCY RANGE (MHz) | UNBALANCE<br>IMPEDANCE | BALANCE<br>IMPEDANCE |  |

|--------------|------------------|-----------------------|------------------------|----------------------|--|

| Murata       | LDB211G8005C-001 | 1800 ±100 MHz         | 50 Ω                   | 50 Ω                 |  |

| Murata       | LDB211G9005C-001 | 1900 ±100 MHz         | 50 Ω                   | 50 Ω                 |  |

| Table 6. Recomme | nded RF B | Balun Devices |

|------------------|-----------|---------------|

|------------------|-----------|---------------|

#### ADC INTERFACE

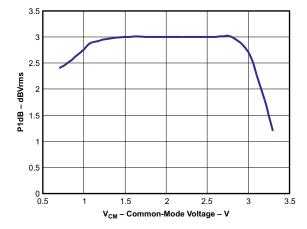

The TRF3710 has an integrated ADC driver buffer that allows direct connection to an analog-to-digital converter (ADC) without additional active circuitry. The common-mode voltage generated by the ADC can be directly supplied to the TRF3710 through the VCMI/Q pins (pins 24, 37). Otherwise, a nominal common-mode voltage of 1.5 V should be applied to those pins. The TRF3710 device can operate with a common-mode voltage from 1.5 V to 2.8 V without any impairment to the output performance. Figure 36 illustrates the degradation of the output compression point as the common mode voltage exceeds those values.

Copyright © 2007–2008, Texas Instruments Incorporated

Figure 36. P1dB Performance vs Common-Mode Voltage

#### APPLICATION FOR A HIGH-PERFORMANCE RF RECEIVER SIGNAL CHAIN

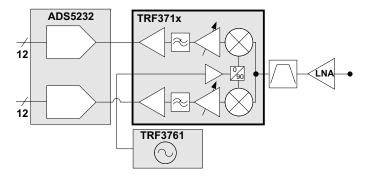

The TRF3710 is the centerpiece component in a high-performance direct downconverting receiver. The device is a highly integrated direct downconverting demodulator that requires minimal additional devices to complete the signal chain. A signal chain block diagram example is shown in Figure 37.

Figure 37. Block Diagram of Direct Downconverting Receiver

The lineup requires a low-noise amplifier (LNA) that operates at the frequency of interest with typical 1-db to 2-dB noise-figure (NF) performance. An RF band-pass filter (BPF) is selected at the frequency band of interest to eliminate unwanted signals and images outside the band from reaching the demodulator. The TRF3710 incorporates the direct downconverter demodulation, baseband filtering, and baseband gain control functions. An external synthesizer, such as the TRF3761, provides the local oscillator (LO) source to the TRF3710. The differential outputs of the TRF3761 directly mate with the LO inputs of the TRF3710. The quadrature outputs (I/Q) of the TRF3710 directly drive the input to the ADC. A dual ADC such as the ADS5232 12-bit, 65-MSPS ADC mates perfectly with the differential I/Q output of the TRF3710. In addition, the common-mode output voltage generated by the ADS5232 is fed directly into the common-mode ports (pins 24, 37) to ensure the optimum dynamic range of the ADC is maintained.

The cascaded performance of the TRF3710 with the ADS5232 and the TRF3761 was measured with WCDMA modulated signals. A single channel WCDMA receive signal was injected into the TRF3710 at -100 dBm. This power roughly corresponds to typical levels this device would see at sensitivity when an appropriate LNA and filter are used. The error-vector magnitude (EVM) of the RX channel was measured as a gauge of the system performance. The EVM percentage at -100 dBm is approximately 27.6% at 60 ksym/s. This result correlates with the required signal-to-noise ratio (SNR) for the device with an appropriate LNA to meet or exceed the bit error rate (BER) specification of 0.1% according to the standards at the input sensitivity level.

#### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples  |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|----------|

|                  |               |              |                    |      |                |                 | (6)                           |                     |              |                         |          |

| TRF3710IRGZR     | ACTIVE        | VQFN         | RGZ                | 48   | 2500           | RoHS & Green    | NIPDAUAG                      | Level-3-260C-168 HR | -40 to 85    | TRF                     | Samples  |

|                  |               |              |                    |      |                |                 |                               |                     |              | 3710                    | Samples  |

| TRF3710IRGZT     | ACTIVE        | VQFN         | RGZ                | 48   | 250            | RoHS & Green    | NIPDAUAG                      | Level-3-260C-168 HR | -40 to 85    | TRF                     | Same las |

|                  |               |              |                    |      |                |                 |                               |                     |              | 3710                    | Samples  |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

23-Apr-2022

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

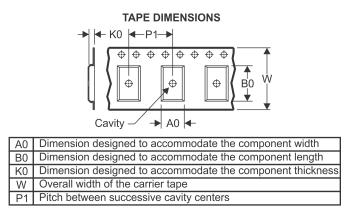

#### TAPE AND REEL INFORMATION

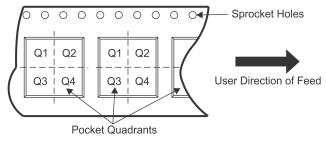

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TRF3710IRGZR                | VQFN            | RGZ                | 48 | 2500 | 330.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

| TRF3710IRGZT                | VQFN            | RGZ                | 48 | 250  | 180.0                    | 16.4                     | 7.3        | 7.3        | 1.5        | 12.0       | 16.0      | Q2               |

TEXAS INSTRUMENTS

www.ti.com

# PACKAGE MATERIALS INFORMATION

12-Feb-2019

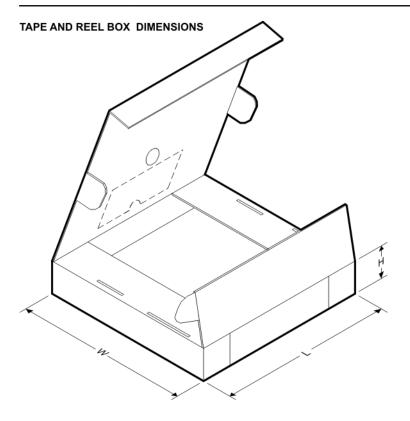

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TRF3710IRGZR | VQFN         | RGZ             | 48   | 2500 | 350.0       | 350.0      | 43.0        |  |

| TRF3710IRGZT | VQFN         | RGZ             | 48   | 250  | 213.0       | 191.0      | 55.0        |  |

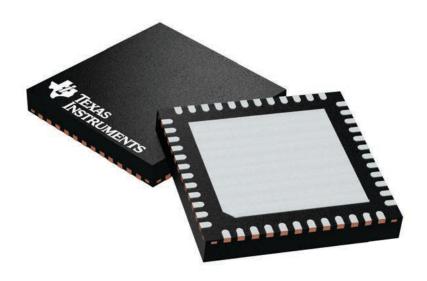

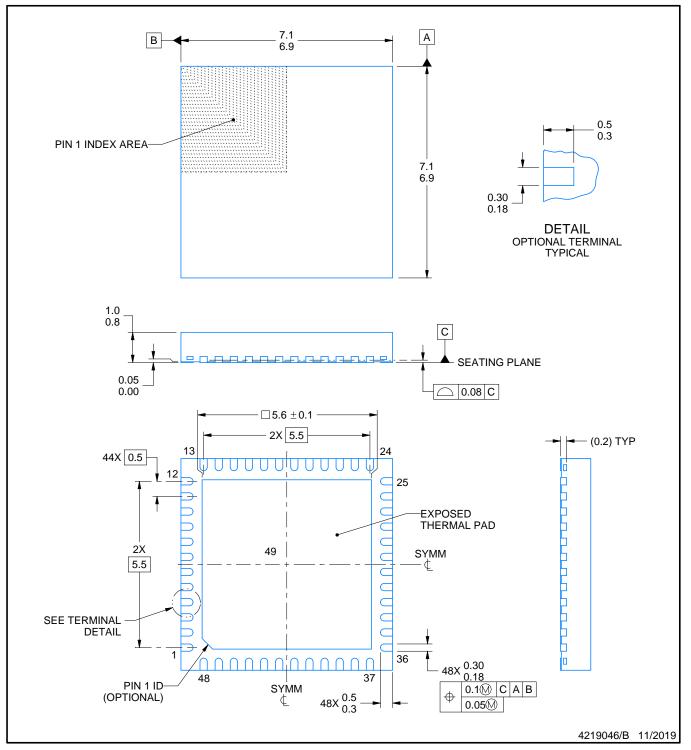

# **RGZ 48**

7 x 7, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

# VQFN - 1 mm max height

PLASTIC QUADFLAT PACK- NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

# **RGZ0048D**

# **PACKAGE OUTLINE**

### VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

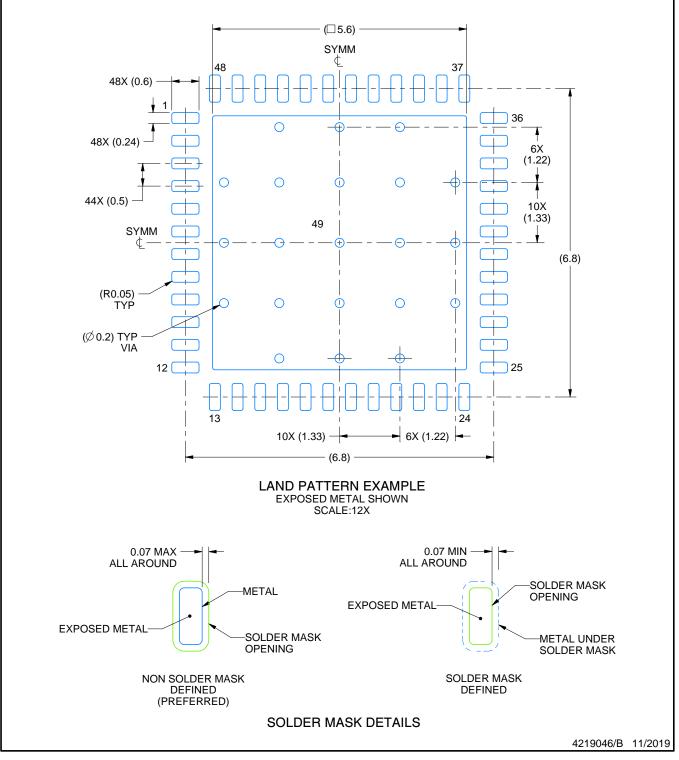

# **RGZ0048D**

# **EXAMPLE BOARD LAYOUT**

### VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

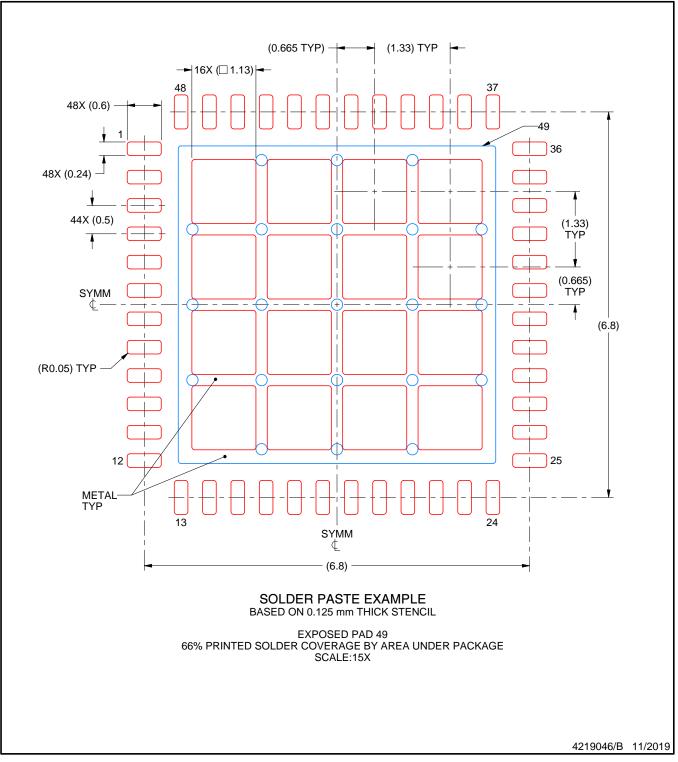

# **RGZ0048D**

# **EXAMPLE STENCIL DESIGN**

### VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated